平成26年2月19日判決言渡 同日原本領収 裁判所書記官 平成25年(行ケ)第10104号 審決取消請求事件 口頭弁論終結日 平成26年1月15日

判

| 原        |     | 告 | エル | ジー  | ディスプレ | 1 |

|----------|-----|---|----|-----|-------|---|

|          |     |   | カン | パニー | リミテッ  | ド |

|          |     |   |    |     |       |   |

| 訴訟代理人弁理士 |     |   | 曾  | 我   | 道     | 治 |

| 同        |     |   | 梶  | 並   |       | 順 |

| 同        |     |   | 上  | 田   | 俊     | _ |

| 同        |     |   | 吉  | 田   | 潤一    | 郎 |

| 同        |     |   | 武  | 井   | 義     | _ |

|          |     |   |    |     |       |   |

| 被        |     | 告 | 特  | 許   | 庁 長   | 官 |

| 指        | 定代理 | 人 | 池  | 渕   |       | 立 |

| 同        |     |   | 近  | 藤   | 幸     | 浩 |

| 同        |     |   | 稲  | 葉   | 和     | 生 |

| 同        |     |   | Щ  | 田   | 和     | 彦 |

|          | 主   | 文 |    |     |       |   |

- 1 原告の請求を棄却する。

- 2 訴訟費用は原告の負担とする。

- 3 この判決に対する上告及び上告受理の申立てのための付加期間を30日と定める。

事実及び理由

第1 請求

特許庁が不服2011-20230号事件について平成24年11月28日にした審決を取り消す。

#### 第2 事案の概要

- 1 特許庁における手続の経緯等

- (1) 原告は、発明の名称を「液晶表示装置用アレイ基板及びその製造方法、液晶表示装置用薄膜トランジスタ及びその製造方法並びに液晶表示装置」とする発明につき、平成18年6月27日に特許出願(特願2006-177137。請求項の数4。優先権主張日:平成17年(2005年)9月30日(大韓民国))を行った。なお、平成22年9月1日付け手続補正書(甲5)により、発明の名称が「液晶表示装置用アレイ基板の製造方法液晶表示装置用アレイ基板の製造方法」に補正されている。

- (2) 原告は、平成23年6月21日付けで拒絶査定を受けたので、同年9月2 0日、これに対する不服の審判を請求するとともに、同日付け手続補正書(甲7) により、手続補正(以下「本件補正」という。)をした。

- (3) 特許庁は、上記請求を不服2011-20230号事件として審理し、平成24年11月28日、本件補正を却下した上、「本件審判の請求は、成り立たない。」との審決(以下「本件審決」という。)をし、同年12月11日、その謄本が原告に送達された。

- (4) 原告は、平成25年4月10日、本件審決の取消しを求めて本件訴訟を提起した。

- 2 特許請求の範囲の記載

- (1) 本件補正前の特許請求の範囲請求項1の記載は、以下のとおりである(ただし、平成23年3月24日付け手続補正書(甲6)による補正後のものである。 以下、請求項1に係る発明を「本願発明」という。)。

基板の非表示領域に、アクティブ領域及び前記アクティブ領域の両側面のオーミックコンタクト領域が定義された第1半導体層、並びにアクティブ領域、前記アク

ティブ領域の両側面の低ドーピング領域,及び前記低ドーピング領域の両外側面の オーミックコンタクト領域が定義された第2半導体層を形成するとともに,前記基 板の表示領域に,アクティブ領域,前記アクティブ領域の両側面の低ドーピング領 域,及び前記低ドーピング領域の両外側面のオーミックコンタクト領域が定義され た第3半導体層,並びに第4半導体層を形成する工程と;

第1フォトレジストパターンをドーピングマスクとして,前記第2半導体層,及び第3半導体層のオーミックコンタクト領域,並びに前記第4半導体層を高濃度 n型の不純物でドーピングする工程と,

前記第1半導体層,第2半導体層,第3半導体層,及び第4半導体層が形成された基板上に,ゲート絶縁膜を形成する工程と,

前記ゲート絶縁膜上に,前記第1半導体層,第2半導体層,及び第3半導体層のアクティブ領域に各々対応する第1ゲート電極,第2ゲート電極,及び第3ゲート電極,並びに前記第4半導体層に対応するストレージ電極を形成するとともに,前記表示領域に,ゲート配線を形成する工程と,

第2フォトレジストパターン及び前記第1ゲート電極をドーピングマスクとして, 前記第1半導体層のオーミックコンタクト領域に高濃度p型の不純物をドーピング する工程と,

前記第1ゲート電極,第2ゲート電極,第3ゲート電極,及びストレージ電極を ドーピングマスクとして,前記第2半導体層,及び第3半導体層の低ドーピング領域に低濃度n型の不純物をドーピングする工程と,

前記第1ゲート電極,第2ゲート電極,第3ゲート電極,及びストレージ電極,並びに前記ゲート配線が形成された基板上に,前記第1半導体層を露出させる第1コンタクトホール,及び第2コンタクトホール,前記第2半導体層を露出させる第3コンタクトホール,及び第4コンタクトホール,並びに前記第3半導体層を露出させる第5コンタクトホール,及び第6コンタクトホールを含む層間絶縁膜を形成する工程と,

前記層間絶縁膜上に,前記第1コンタクトホール,及び第2コンタクトホールを通じて前記第1半導体層と各々接触する第1ソース電極及び第1ドレイン電極,前記第3コンタクトホール,及び第4コンタクトホールを通じて前記第2半導体層と各々接触する第2ソース電極及び第2ドレイン電極,前記第5コンタクトホール,及び第6コンタクトホールを通じて前記第3半導体層と各々接触する第3ソース電極及び第3ドレイン電極,並びに前記表示領域に画素領域を定義し,前記ゲート配線と交差するデータ配線を形成する工程と.

前記第1ソース電極,第2ソース電極,及び第3ソース電極,前記第1ドレイン電極,第2ドレイン電極,及び第3ドレイン電極並びに前記データ配線が形成された基板上に,前記第3ドレイン電極を露出させるドレインコンタクトホールを含む保護層を形成する工程と,

前記保護層上に,前記ドレインコンタクトホールを通じて前記第3ドレイン電極と接触するように前記画素領域に位置する画素電極を形成する工程と を含むことを特徴とする液晶表示装置用アレイ基板の製造方法。

(2) 本件補正後の特許請求の範囲請求項1の記載は、以下のとおりである(甲7)。なお、下線は、本件補正による補正個所である。以下、請求項1に係る発明を「本件補正発明」といい、その明細書(甲4~7)を「本件補正明細書」という。基板の非表示領域に、アクティブ領域及び前記アクティブ領域の両側面のオーミックコンタクト領域が定義された第1半導体層、並びにアクティブ領域の両外側面のオーミックコンタクト領域が定義された第2半導体層を形成するとともに、前記基板の表示領域に、アクティブ領域、前記アクティブ領域の両側面の低ドーピング領域、前記アクティブ領域の両側面の低ドーピング領域、及び前記低ドーピング領域の両外側面のオーミックコンタクト領域が定義された第3半導体層、並びに第4半導体層を形成する工程と:

前記第1半導体層全部と前記第2及び第3半導体層のアクティブ領域と低濃度ド ーピング領域を覆い前記第2及び第3半導体層のオーミックコンタクト領域及び前 記第4半導体層全部を露出させる第1フォトレジストパターンをドーピングマスク として、前記第2半導体層及び第3半導体層のオーミックコンタクト領域、並びに 前記第4半導体層を高濃度n型の不純物でドーピングする第1ドーピング工程と、

前記第1フォトレジストパターンを除去する工程と,

前記第1半導体層,第2半導体層,第3半導体層,及び第4半導体層が形成された基板上に,ゲート絶縁膜を形成する工程と,

前記ゲート絶縁膜上に,前記第1半導体層,第2半導体層,及び第3半導体層のアクティブ領域に各々対応する第1ゲート電極,第2ゲート電極,及び第3ゲート電極,並びに前記第4半導体層に対応するストレージ電極を形成するとともに,前記表示領域に,ゲート配線を形成する工程と,

前記第1半導体層全部を露出させて前記第2ないし第4半導体層全部を覆う第2フォトレジストパターン及び前記第1ゲート電極をドーピングマスクとして,前記第1半導体層のオーミックコンタクト領域に高濃度p型の不純物をドーピングする第2ドーピング工程と,

前記第2フォトレジストパターンを除去する工程と,

前記第1ゲート電極,第2ゲート電極,第3ゲート電極,及びストレージ電極を ドーピングマスクとして,前記第2半導体層,及び第3半導体層の低ドーピング領域に低濃度n型の不純物をドーピングする<u>第3ドーピング</u>工程と,

前記第1ゲート電極,第2ゲート電極,第3ゲート電極,及びストレージ電極,並びに前記ゲート配線が形成された基板上に,前記第1半導体層を露出させる第1コンタクトホール,及び第2コンタクトホール,前記第2半導体層を露出させる第3コンタクトホール,及び第4コンタクトホール,並びに前記第3半導体層を露出させる第5コンタクトホール,及び第6コンタクトホールを含む層間絶縁膜を形成する工程と,

前記層間絶縁膜上に,前記第1コンタクトホール,及び第2コンタクトホールを 通じて前記第1半導体層と各々接触する第1ソース電極及び第1ドレイン電極,前 記第3コンタクトホール,及び第4コンタクトホールを通じて前記第2半導体層と各々接触する第2ソース電極及び第2ドレイン電極,前記第5コンタクトホール,及び第6コンタクトホールを通じて前記第3半導体層と各々接触する第3ソース電極及び第3ドレイン電極,並びに前記表示領域に画素領域を定義し,前記ゲート配線と交差するデータ配線を形成する工程と,

前記第1ソース電極,第2ソース電極,及び第3ソース電極,前記第1ドレイン電極,第2ドレイン電極,及び第3ドレイン電極並びに前記データ配線が形成された基板上に,前記第3ドレイン電極を露出させるドレインコンタクトホールを含む保護層を形成する工程と,

前記保護層上に,前記ドレインコンタクトホールを通じて前記第3ドレイン電極 と接触するように前記画素領域に位置する画素電極を形成する工程と

でなることを特徴とする液晶表示装置用アレイ基板の製造方法。

- 3 本件審決の理由の要旨

- (1) 本件審決の理由は、別紙審決書(写し)記載のとおりであり、要するに、①本件補正発明は、後記工及び才の周知例1及び2に記載された周知技術を勘案することにより、後記アないしウの引用例1ないし3に記載された発明に基づいて当業者が容易に発明をすることができたものであり、特許法29条2項の規定により特許出願の際独立して特許を受けることができるものではなく、平成18年法律第55号による改正前の特許法(以下「法」という。)17条の2第5項において準用する法126条5項の規定に違反するから、本件補正は、法159条1項において読み替えて準用する法53条1項の規定により却下すべきものであり、②本願発明も、周知例1及び2に記載された周知技術を勘案することにより、引用例1ないし3に記載された発明に基づいて当業者が容易に発明をすることができたものであり、特許法29条2項の規定により、特許を受けることができない、というものである。

ア 引用例1:特開平9-172183号公報(甲1)

イ 引用例2:特開2004-303791号公報(甲2)

ウ 引用例3:特開平5-235360号公報(甲3)

工 周知例1:特開2005-223347号公報(甲8)

才 周知例2:特開平9-105953号公報(乙1)

(2) 本件審決が認定した引用例1に記載された発明(以下「引用発明」という。)並びに本件補正発明と引用発明との一致点及び相違点は,以下のとおりである。

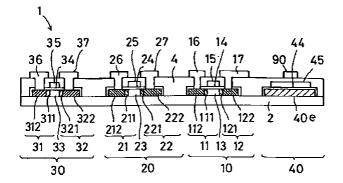

ア 引用発明:同一の絶縁基板2の上に,第一導電型の画素用TFT10,第一 導電型の駆動回路用TFT20,第二導電型の駆動回路用TFT30,及び保持容 量40が形成されて,

信号線90及び走査線91で区画形成され,第一導電型の画素用TFT10を介して画像信号が入力される液晶セルの液晶容量94及び保持容量40が存在する画素領域を有するアクティブマトリクス部81,並びに,

それぞれ第二導電型の駆動回路用TFT30及び第一導電型の駆動回路用TFT20を備えるデータドライバ部82及び走査ドライバ部83,

が形成された,アクティブマトリクス基板1の形成方法であって,

絶縁基板2の表面に、それぞれ第一導電型の画素用TFT10、第一導電型の駆動回路用TFT20、第二導電型の駆動回路用TFT30、及び保持容量40を形成するためのものである島状のシリコン膜10a、20a、30a及び40aを形成するシリコン膜形成工程、

ゲート絶縁膜14,24,34,及び誘電体膜44を形成するゲート絶縁膜形成工程,

約 $1 \times 10^{12}$  c m $^{-2}$ のドーズ量でボロンイオン(第二導電型不純物)を打ち込んでチャネルドープを行なうチャネルドープ工程、

第二導電型の駆動回路用TFT30の形成領域を覆うと共に、第一導電型の画素用TFT10及び第一導電型の駆動回路用TFT20について後にそれぞれ形成す

るゲート電極15,25の形成予定領域を広めに覆うレジストマスク601を形成 する1回目のマスク形成工程,

レジストマスク601をマスクとして第一導電型不純物を約 $1 \times 10^{15}$  c m<sup>-2</sup> のドーズ量でイオン注入し,その結果,低濃度第二導電型のシリコン膜10 a , 20 a の内,リンイオンが打ち込まれた領域は,導電型が反転して不純物濃度が約 $1 \times 10^{20}$  c m<sup>-3</sup>の高濃度ソース・ドレイン領域112 , 122 , 212 , 222 となり,低濃度第二導電型のシリコン膜40 a も,導電型が反転して不純物濃度が約 $1 \times 10^{20}$  c m<sup>-3</sup>の高濃度第一導電型の下層側電極部40 d となる高濃度第一導電型不純物導入工程,

レジストマスク601を除去する工程,

第一導電型の画素用TFT10,第一導電型の駆動回路用TFT20及び第二導電型の駆動回路用TFT30それぞれのゲート電極15,25及び35,並びに上層側電極部45を形成するゲート電極形成工程,

第一導電型の画素用TFT10,第一導電型の駆動回路用TFT20,及び保持容量40の形成領域を覆うレジストマスク602を形成する2回目のマスク形成工程,

ボロンイオンを約 $3\times10^{13}$  c m $^{-2}$ のドーズ量でイオン注入し,その結果,低濃度第二導電型のシリコン膜30 a には,ゲート電極35 に対して自己整合的に不純物濃度が約 $3.1\times10^{18}$  c m $^{-3}$ の低濃度第二導電型のソース・ドレイン領域31, 32が形成され,不純物が導入されなかった部分がチャネル領域33となる低濃度第二導電型不純物導入工程,

レジストマスク602を除去する工程、

第一導電型の画素用TFT10,第一導電型の駆動回路用TFT20,及び保持容量40の形成領域を覆うと共に,第二導電型の駆動回路用TFT30のゲート電極35を広めに覆うレジストマスク603を形成する3回目のマスク形成工程,

ボロンイオンを約 $1 \times 10^{15}$  c m<sup>-2</sup>のドーズ量でイオン注入し、その結果、低

濃度第二導電型のソース・ドレイン領域 3 1, 3 2には不純物濃度が  $1 \times 1$  0  $^{20}$  c  $m^{-3}$  の高濃度ソース・ドレイン領域 3 1 2, 3 2 2 が形成され,低濃度第二導電型のソース・ドレイン領域 3 1, 3 2 の内,レジストマスク 6 0 3 で覆われていた部分はそのまま不純物濃度が約 2.  $1 \times 1$  0  $^{18}$  c  $m^{-3}$  の低濃度ソース・ドレイン領域 3 1 1, 3 2 1 となって,第二導電型の駆動回路用TFT 3 0 を形成する高濃度第二導電型不純物導入工程,

レジストマスク603を除去する工程,

レジストマスクを形成する事なく,リンイオンを約 $1 \times 10^{13}$  c m $^{-2}$ のドーズ量でイオン注入し,その結果,高濃度ソース・ドレイン領域112,122,212,222 に挟まれた低濃度第二導電型のシリコン膜10a,20a には,ゲート電極15,25 に対して自己整合的に不純物濃度が約 $0.9 \times 10^{18}$  c m $^{-3}$  の低濃度ソース・ドレイン領域111,121,211,221が形成され,不純物が導入されなかった部分がチャネル領域23,13 となり,第一導電型の画素用TFT10及び第一導電型の駆動回路用TFT20を形成する低濃度第一導電型不純物導入工程,

層間絶縁膜4を形成する工程,

層間絶縁膜4を形成した後、活性化のためのアニールを行う工程、

層間絶縁膜4に,各TFTの高濃度ソース・ドレイン領域312,322,21 2,222,112,122につながる各コンタクトホールを形成する工程,及び 信号線や画素電極などとともに前記各コンタクトホールに各ソース・ドレイン電 極36,37,26,27,16,17を形成する工程,

からなるアクティブマトリクス基板1の形成方法。

イ 一致点:基板の非表示領域に、アクティブ領域及び前記アクティブ領域の両側のオーミックコンタクト領域が定義された第1半導体層、並びにアクティブ領域、前記アクティブ領域の両側面の低ドーピング領域、及び前記低ドーピング領域の両外側面のオーミックコンタクト領域が定義された第2半導体層を形成するとともに、

前記基板の表示領域に、アクティブ領域、前記アクティブ領域の両側面の低ドーピング領域、及び前記低ドーピング領域の両外側面のオーミックコンタクト領域が定義された第3半導体層,並びに第4半導体層を形成する工程と;

前記第1半導体層全部と前記第2及び第3半導体層のアクティブ領域と低濃度ドーピング領域を覆い前記第2及び第3半導体層のオーミックコンタクト領域及び前記第4半導体層全部を露出させる第1フォトレジストパターンをドーピングマスクとして,前記第2半導体層及び第3半導体層のオーミックコンタクト領域,並びに前記第4半導体層を高濃度n型の不純物でドーピングする第1ドーピング工程と,

前記第1フォトレジストパターンを除去する工程と,

前記第1半導体層,第2半導体層,第3半導体層,及び第4半導体層が形成された基板上に,ゲート絶縁膜を形成する工程と,

前記ゲート絶縁膜上に,前記第1半導体層,第2半導体層,及び第3半導体層のアクティブ領域に各々対応する第1ゲート電極,第2ゲート電極,及び第3ゲート電極,並びに前記第4半導体層に対応するストレージ電極を形成する工程と,

前記第1半導体層を露出させて前記第2ないし第4半導体層全部を覆う第2フォトレジストパターンをドーピングマスクとして,前記第1半導体層のオーミックコンタクト領域に高濃度p型の不純物をドーピングする第2ドーピング工程と,

前記第2フォトレジストパターンを除去する工程と,

前記第1ゲート電極,第2ゲート電極,第3ゲート電極,及びストレージ電極を ドーピングマスクとして,前記第2半導体層,及び第3半導体層の低ドーピング領域に低濃度n型の不純物をドーピングする第3ドーピング工程と,

前記第1ゲート電極,第2ゲート電極,第3ゲート電極,及びストレージ電極, 並びに前記ゲート配線が形成された基板上に,前記第1半導体層を露出させる第1 コンタクトホール,及び第2コンタクトホール,前記第2半導体層を露出させる第 3コンタクトホール,及び第4コンタクトホール,並びに前記第3半導体層を露出 させる第5コンタクトホール,及び第6コンタクトホールを含む層間絶縁膜を形成 する工程と,

前記層間絶縁膜上に,前記第1コンタクトホール,及び第2コンタクトホールを通じて前記第1半導体層と各々接触する第1ソース電極及び第1ドレイン電極,前記第3コンタクトホール,及び第4コンタクトホールを通じて前記第2半導体層と各々接触する第2ソース電極及び第2ドレイン電極,前記第5コンタクトホール,及び第6コンタクトホールを通じて前記第3半導体層と各々接触する第3ソース電極及び第3ドレイン電極,並びに前記表示領域に画素領域を定義し,前記ゲート配線と交差するデータ配線を形成する工程と,

を含むことを特徴とする液晶表示装置用アレイ基板の製造方法。

ウ 相違点1:本件補正発明においては、「アクティブ領域及び前記アクティブ 領域の両側面のオーミックコンタクト領域が定義された第1半導体層」が形成され るのに対して、引用発明においては、「第一導電型の画素用TFT10,第一導電 型の駆動回路用TFT20、及び保持容量40の形成領域を覆うレジストマスク6 02を形成する2回目のマスク形成工程,ボロンイオンを約 $3\times10^{13}$  c m<sup>-2</sup>の ドーズ量でイオン注入し、その結果、低濃度第二導電型のシリコン膜30aには、 ゲート電極 35 に対して自己整合的に不純物濃度が約  $3.1 \times 10^{18}$  c m<sup>-3</sup>の低 濃度第二導電型のソース・ドレイン領域31,32が形成され、不純物が導入され なかった部分がチャネル領域33となる低濃度第二導電型不純物導入工程、レジス トマスク602を除去する工程,第一導電型の画素用TFT10,第一導電型の駆 動回路用TFT20,及び保持容量40の形成領域を覆うと共に,第二導電型の駆 動回路用TFT30のゲート電極35を広めに覆うレジストマスク603を形成す る3回目のマスク形成工程,ボロンイオンを約 $1 \times 10^{15}$  c m<sup>-2</sup>のドーズ量でイ オン注入し、その結果、低濃度第二導電型のソース・ドレイン領域31、32には 不純物濃度が  $1 \times 1$   $0^{20}$  c  $m^{-3}$  の高濃度ソース・ドレイン領域 3 1 2 , 3 2 2 が 形成され、低濃度第二導電型のソース・ドレイン領域31、32の内、レジストマ スク603で覆われていた部分はそのまま不純物濃度が約2. $1 \times 10^{18} \text{ cm}^{-3}$  の低濃度ソース・ドレイン領域311,321となって,第二導電型の駆動回路用TFT30を形成する高濃度第二導電型不純物導入工程」を備えることから,駆動回路用TFT30についても,低濃度第二導電型のソース・ドレイン領域31,32及び高濃度ソース・ドレイン領域312,322が形成され,不純物が導入されなかった部分がチャネル領域33となるものであり,本件補正発明の「アクティブ領域」に対応する引用発明の「チャネル領域33」の両側面には低濃度ソース・ドレイン領域311,321が配され,その両外側面に本件補正発明の「オーミックコンタクト領域」に対応する「高濃度ソース・ドレイン領域312,322」が配されることとなることから,本件補正発明に係る「アクティブ領域の両側面のオーミックコンタクト領域が定義された第1半導体層」が形成されない点。

工 相違点2:本件補正発明においては、「前記ゲート絶縁膜上に、前記第1半導体層、第2半導体層、及び第3半導体層のアクティブ領域に各々対応する第1ゲート電極、第2ゲート電極、及び第3ゲート電極、並びに前記第4半導体層に対応するストレージ電極を形成するとともに、前記表示領域に、ゲート配線を形成する工程」を備えるのに対して、引用発明においては、完成品である「アクティブマトリクス基板1」は本件補正発明の「ゲート配線」に対応する「走査線91」を備え、また、本件補正発明の「前記ゲート絶縁膜上に、前記第1半導体層、第2半導体層、及び第3半導体層のアクティブ領域に各々対応する第1ゲート電極、第2ゲート電極、及び第3ゲート電極、並びに前記第4半導体層に対応するストレージ電極を形成する工程」に相当する工程を有するものの、当該工程において各電極を形成する「とともに、前記表示領域に、ゲート配線を形成する」構成を有することが明らかでない点。

オ 相違点3:本件補正発明においては、「前記第1ソース電極、第2ソース電極、及び第3ソース電極、前記第1ドレイン電極、第2ドレイン電極、及び第3ドレイン電極並びに前記データ配線が形成された基板上に、前記第3ドレイン電極を露出させるドレインコンタクトホールを含む保護層を形成する工程と、

前記保護層上に,前記ドレインコンタクトホールを通じて前記第3ドレイン電極 と接触するように前記画素領域に位置する画素電極を形成する工程と」を備えるが, 引用発明においてはそのような工程を備えない点。

カ 相違点4:本件補正発明は、「前記第1半導体層全部を露出させて前記第2 ないし第4半導体層全部を覆う第2フォトレジストパターン及び前記第1ゲート電 極をドーピングマスクとして、前記第1半導体層のオーミックコンタクト領域に高 濃度p型の不純物をドーピングする第2ドーピング工程」を有するが、引用発明に おいては「第一導電型の画素用TFT10,第一導電型の駆動回路用TFT20, 及び保持容量40の形成領域を覆うと共に、第二導電型の駆動回路用TFT30の ゲート電極35を広めに覆うレジストマスク603を形成する3回目のマスク形成 工程」及び「ボロンイオンを約 $1 \times 10^{15}$  c m<sup>-2</sup>のドーズ量でイオン注入し、そ の結果、低濃度第二導電型のソース・ドレイン領域31、32には不純物濃度が1  $\times$ 10<sup>20</sup> c m<sup>-3</sup>の高濃度ソース・ドレイン領域312,322が形成され、低濃 度第二導電型のソース・ドレイン領域31,32の内,レジストマスク603で覆 われていた部分はそのまま不純物濃度が約2. $1 \times 10^{18} \, \mathrm{cm}^{-3}$ の低濃度ソース ・ドレイン領域311、321となって、第二導電型の駆動回路用TFT30を形 成する高濃度第二導電型不純物導入工程」を備えることから、「前記第1半導体層 を露出させて前記第2ないし第4半導体層全部を覆う第2フォトレジストパターン をドーピングマスクとして,前記第1半導体層のオーミックコンタクト領域に高濃 度 p 型の不純物をドーピングする第 2 ドーピング工程 | に対応する構成を有すると はいえるものの,本件補正発明のように,前記第1半導体層に対する高濃度p型の 不純物のドーピングが、「前記第1半導体層全部を露出させて」「前記第1ゲート 電極をドーピングマスクとして、前記第1半導体層のオーミックコンタクト領域 に」なされるものではない点。

キ 相違点 5:本件補正発明は、本件補正後の請求項1に記載された各工程「でなることを特徴とする」製造方法であるのに対して、引用発明においては、前記請

求項1に記載された各工程のいずれにも対応しない工程である、「約 $1 \times 10^{12}$  c m<sup>-2</sup>のドーズ量でボロンイオン (第二導電型不純物) を打ち込んでチャネルドー プを行なうチャネルドープ工程」、「ボロンイオンを約 $3 \times 10^{13} \text{ cm}^{-2}$ のドー ズ量でイオン注入し、その結果、低濃度第二導電型のシリコン膜30aには、ゲー ト電極35に対して自己整合的に不純物濃度が約3.1×10<sup>18</sup>cm<sup>-3</sup>の低濃度 第二導電型のソース・ドレイン領域31,32が形成され、不純物が導入されなか った部分がチャネル領域33となる低濃度第二導電型不純物導入工程,」「第一導 電型の画素用TFT10,第一導電型の駆動回路用TFT20,及び保持容量40 の形成領域を覆うと共に、第二導電型の駆動回路用TFT30のゲート電極35を 広めに覆うレジストマスク603を形成する3回目のマスク形成工程」、「ボロン イオンを約 $1 \times 10^{15}$  c m<sup>-2</sup>のドーズ量でイオン注入し、その結果、低濃度第二 導電型のソース・ドレイン領域 31, 32 には不純物濃度が  $1 \times 10^{20}$  c m<sup>-3</sup>の 高濃度ソース・ドレイン領域312,322が形成され、低濃度第二導電型のソー ス・ドレイン領域31,32の内,レジストマスク603で覆われていた部分はそ のまま不純物濃度が約2.  $1 \times 10^{18} \, \text{cm}^{-3}$ の低濃度ソース・ドレイン領域31 1,321となって、第二導電型の駆動回路用TFT30を形成する高濃度第二導 電型不純物導入工程」、「レジストマスク603を除去する工程」及び「層間絶縁 膜4を形成した後、活性化のためのアニールを行う工程」を備えている点。

4 取消事由

本件補正発明の容易想到性に係る判断の誤り

- (1) 一致点の認定の誤り

- (2) 相違点5の判断の誤り

#### 第3 当事者の主張

[原告の主張]

- 1 一致点の認定の誤り

- (1) 本件審決は、引用発明の「ゲート絶縁膜14,24,34,及び誘電体膜

44を形成するゲート絶縁膜形成工程」は、本件補正発明の「前記第1半導体層、第2半導体層、第3半導体層、及び第4半導体層が形成された基板上に、ゲート絶縁膜を形成する工程」に相当するとした上で、本件補正発明と引用発明とは、「第1ドーピング工程」の後に「ゲート絶縁膜を形成する工程」が行われる点で一致すると認定した。

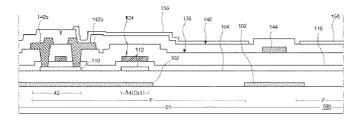

しかし、本件補正発明における第1ドーピング工程(n+ドーピング) はゲート 絶縁膜(別紙1記載の図10Dの符号116) が形成されない状態で行われ(別紙1記載の図10C及び図11C参照) 、その後、ゲート絶縁膜116とゲート電極を 形成して第2ドーピング工程(p+ドーピング) が行われる。

他方、別紙 2 記載の引用例 1 の図 1 6 (b) に示されるドーピング工程(これは本件補正発明の第 1 ドーピング工程に対応する「n + ドーピング」である。)は、ゲート絶縁膜 1 4 , 2 4 , 3 4 及び誘電体膜 4 4 (図 1 6 (a) 参照)が形成された後に行われるものである(甲 1 【 0 2 8 8 】 【 0 2 8 9 】)。

すなわち、本件補正発明では、「第1ドーピング工程」の後に「ゲート絶縁膜を 形成する工程」が行われるが、引用発明では、逆に、「ゲート絶縁膜を形成する工程」の後に「ドーピング工程」が行われる。引用発明のようにゲート絶縁膜が形成 された後に行われるドーピング工程と、本件補正発明のようにゲート絶縁膜が形成 されない状態で行われる第1ドーピング工程とを比較すると、引用発明において、 本件補正発明と同等のドーピング濃度及びドーピング深さを得るためには、ドーピ ング工程のために本件補正発明より大きな消費電力が必要であり、同じ消費電力で は本件補正発明と同等のドーピング濃度及びドーピング深さを得ることができない。

したがって、ゲート絶縁膜の形成工程において、本件補正発明と引用発明とは、 明白な相違点を有するものである。

よって、本件審決の一致点の認定は誤りである。

(2) 被告の主張について

ア 被告は、本件補正明細書全体の記載を見ても、第1ドーピング工程を行った

後にゲート絶縁膜形成工程を行う工程順序に限定すべきとの記載やそのような工程 順序とすることに技術的意義があるとの記載はないと主張する。

しかし、本件補正発明は、製造方法に関する発明であり、図10A~Jや図11A~Jを用いて、各工程順序を明確に規定しており、これ以外の工程順序に関して何ら記載していないのであるから、本件補正明細書に記載された工程順序に限定して解釈するのが当然である。また、本件補正発明に係る請求項において、「第1ドーピング工程」の後に「ゲート絶縁膜形成工程」が記載されているのは、本件補正明細書の実施例として記載された図10A~J及び図11A~Jの工程順序に対応したものであり、一定の時間的順序に従って本件補正発明の製造方法が実施されることは明らかである。特に、被告も認めるように、本件補正明細書(甲4【0034】)では、「図10Dと図11Dに示したように、前記第3マスク工程を行った後、第1基板100全面にゲート絶縁膜116を形成する」と明記されており、このような一定の時間的順序を明記した本件補正明細書の記載を参酌すれば、本件補正発明における請求項1の記載は、「第1ドーピング工程」の後に「ゲート絶縁膜形成工程」が行われる工程順序に限定したものと解釈すべきである。

イ 被告は、本件補正明細書の図10F及び図11Fに示された工程では、ゲート絶縁膜116を介してn<sup>-</sup>イオンのドーピングが行われており、これは、ゲート絶縁膜の形成工程後にn<sup>-</sup>イオンのドーピング工程を行うことを表しているのであるから、「ゲート絶縁膜形成工程」後にn型不純物(nイオン)のドーピング工程を行う方法が本件補正明細書において排除されているとはいえないと主張する。

しかし、本件補正発明において「ゲート絶縁膜形成工程」の前に行われる「第1ドーピング工程」は、請求項1に記載された「高濃度 n型の不純物でドーピングする第1ドーピング工程」であり、被告が指摘する「n-イオンのドーピング」は、請求項1において「ゲート絶縁膜形成工程」の後に行われている「低濃度 n型の不純物をドーピングする第3ドーピング工程」に相当するものである(甲4【0036】【図10F】【図11F】)。

したがって、被告の上記主張は、「第1ドーピング工程」と「第3ドーピング工程」とを混同するものであって、失当である。

ウ 被告は、引用例1(【0288】【0289】)の記載や図4(a)等の記載を挙げて、引用例1には、「ゲート絶縁膜形成工程」と「チャネルドープ工程」(「C/D」工程)が連続して実施される一連の工程として記載されているなどと主張する。

しかし、引用例1(【0288】)の記載は、「シリコン膜形成工程」の後に「ゲート絶縁膜形成工程」を行うことを記載しているにすぎない。

また、引用例1(【0288】等)の記載は、図4(a)等の記載から明らかなとおり、「シリコン膜10a、20a、30a、40aを形成した後(シリコン膜形成工程)、ゲート絶縁膜14、24、34、及び誘電体膜44を形成する」という工程が最初に行われ、その後に表7等に示された6つの代表的な工程が行われる状況を説明するものである。すなわち、チャネルドープ工程(「C/D」工程)が、例えば、引用例1の表7の工程順序1である場合には、「ゲート絶縁膜形成工程」と「チャネルドープ工程」は、連続して実施することとなるが、チャネルドープ工程(「C/D」工程)が、表7の工程順序2あるいは3である場合には、「ゲート絶縁膜形成工程」と「チャネルドープ工程」は、連続して実施されるものではない。ましてや、表7に示された24通りの工程順序のいずれの場合にも、「ゲート絶縁膜形成工程」は、工程順序1の前に行われるものである。

したがって,被告の上記主張は,失当である。

また、引用例1には、「ゲート絶縁膜形成工程」と「チャネルドープ工程」が連続して実施される一連の工程として記載されているということはできない以上、これを前提として、引用例1には「ゲート絶縁膜形成工程」と「第1ドーピング工程」とが工程順序を交換して実施可能であることが記載されているという被告の主張も失当である。

2 相違点5の判断の誤り

(1) 本件審決は、相違点 5 に関し、アクティブマトリクス回路を用いた液晶表示装置の基板について、各TFTを構成するシリコン膜に対してチャネルドープを行わずに製造することは、2 1 (特開平9-105953) にも示されているように、従来から普通に行われている、引用発明は、最小限の製造工程数によって各TFTの電気的特性を向上させた半導体装置とその製造方法及びアクティブマトリクス基板を提供することも課題としている(甲1【0013】)、引用例1の実施例8では、チャネルドープ工程が必須のものである旨の記載も示唆も見いだせないなどとして、引用発明において、製造工程数をより少なくすべく、「約1×10 $^{12}$  cm $^{-2}$  のドーズ量でボロンイオン(第二導電型不純物)を打ち込んでチャネルドープを行なうチャネルドープ工程」を有さないものとすることは当業者が適宜になし得たことであると判断した。

しかし、引用発明において、引用例1の図16(a)に示されたチャネルドープ 工程は必須の構成であり、当該工程を行わないことは、当業者にとって自明な事項 ではない。

すなわち、引用例1の請求項1には、「…該第二導電型薄膜トランジスタは…該 第二チャンネル領域と同じ不純物濃度を有するオフセット領域を具備するオフセット構造を成し、該第二チャンネル領域は極低濃度の第二導電型不純物を含んでいる」と記載され、請求項8にも、「…第二導電型不純物を極低濃度にて半導体膜に導入する極低濃度第二導電型不純物導入工程」と記載されている。

また,引用例1の表1ないし8では,チャネルドープ工程が全てのケースについて必須の工程として明示されている。

したがって、引用発明においては、引用例の図16(a)に示されるチャネルドープ工程が必須の工程であることは明らかであり、当該工程を含む引用発明は、3回のドーピング工程からなる本件補正発明とは明白な差異を有するものである。

そして、引用発明におけるチャネルドープ工程では、イオン(不純物) 注入によって半導体層の結晶性が崩れ、移動度も低下する問題が生じ得るが、本件補正発明

では、チャネルドープ工程なしに3回のドーピング工程だけで成り立つので、チャネルドープによる移動度低下の問題を防止することができるという有利な作用効果を奏するものである。

よって、相違点5に係る本件審決の判断は誤りである。

## (2) 被告の主張について

ア 被告は、本件審決において、引用発明の「チャネルドープ工程」は本件補正 発明と対比・判断する必要がそもそもなかったものであると主張する。

しかし、本件補正発明は、「チャネルドープ工程なしに3回のドーピング工程だけで成り立つ」という技術的意義を有するものである。そして、本件補正発明では、「チャネルドープ工程」を構成要件とせずに、第1ドーピング工程ないし第3ドーピング工程として3回のドーピング工程を明記し、「チャネルドープ工程なしに3回のドーピング工程だけで成り立つ」ことを明確化しているものである。換言すると、チャネルドープ工程を他の工程に置き換えるだけでは、「3回のドーピング工程だけで成り立つ」という本件補正発明の技術的意義は実現できないものであり、「チャネルドープ工程」に関する対比・判断は、本件審決に影響するものである。よって、被告の上記主張は、失当である。

イ 被告は、乙1には、チャネルドープを行わない液晶表示装置の基板の製造方 法が開示されているなどと主張する。

確かに、乙1には、チャネルドープを行わない液晶表示装置の基板の製造方法が 開示されている。

しかし、乙1は、プラズマCVD法あるいはLPCVD法をチャネルドープの代わりに用いる技術を開示しているものにすぎない。チャネル工程を他の工程に置き換えるだけでは、「3回のドーピング工程だけで成り立つ」という本件補正発明の技術的意義を達成することはできない。

したがって、被告の上記主張は、失当である。

ウ 被告は、引用例1(【0149】【0150】)の記載を挙げて、引用発明

では、チャネルドープ工程が不要であると主張する。

しかし、引用例1(【0150】)の「真性のシリコン膜10a、20a、30aを形成した後に、低濃度第二導電型シリコン膜形成工程において低濃度第二導電型の不純物を打ち込む方法に代えて、 $B_2H_6$ と $SiH_6$ との混合ガスを用いて低濃度のボロンをドープしたシリコン膜(ドープトシリコン膜/ドープト半導体膜)を低濃度第二導電型のシリコン膜10a、20a、30aとしてCVD法により形成した後、それにゲート絶縁膜14、24、34を形成し、しかる後に、図4(b)~(d)に示す工程、または図5(b)~(d)に示す工程を行なってもよい。」との記載や図4及び図5の記載から明らかなように、引用例1は、単にチャネルドープの代わりにCVD法を用いることを開示しているにすぎず、CVD法におけるドープと、その後に続けて、図4(b)ないし(d)あるいは図5(b)ないし(d)に記載された3回のドープの合計4回のドーピング工程を必要とするのであるから、「3回のドーピング工程だけで成り立つ」という本件補正発明の技術的意義を達成することはできない。

したがって、被告の上記主張は、失当である。

#### 「被告の主張」

- 1 一致点の認定の誤りについて

- (1) 本件補正発明に係る請求項では、「前記第1半導体層全部と前記第2及び第3半導体層のアクティブ領域と低濃度ドーピング領域を覆い前記第2及び第3半導体層のオーミックコンタクト領域及び前記第4半導体層全部を露出させる第1フォトレジストパターンをドーピングマスクとして、前記第2半導体層及び第3半導体層のオーミックコンタクト領域、並びに前記第4半導体層を高濃度n型の不純物でドーピングする第1ドーピング工程」の後に、「前記第1半導体層、第2半導体層、第3半導体層、及び第4半導体層が形成された基板上に、ゲート絶縁膜を形成する工程」が記載されている。

しかし、本件補正発明は、「第1ドーピング工程」と「ゲート絶縁膜形成工程」

の工程順序について、何ら限定するものではない。

すなわち,前記請求項において,「ゲート絶縁膜形成工程」は,単に,「前記第 1半導体層,第2半導体層,第3半導体層,及び第4半導体層が形成された基板上 に,ゲート絶縁膜を形成する」と記載されているだけであって,当該「ゲート絶縁 膜形成工程」において,ゲート絶縁膜が形成される「前記第1半導体層,第2半導 体層,第3半導体層,及び第4半導体層」が既に「第1ドーピング工程」によって 高濃度n型の不純物がドーピングされたものであるとの限定はない。

また,前記請求項の末尾には,「…工程と,…工程とでなることを特徴とする液晶表示装置用アレイ基板の製造方法」と記載されており,当該請求項全体をみても,「第1ドーピング工程」を行った後に「ゲート絶縁膜形成工程」を行うことに限定される旨の記載を見いだすことはできない。

したがって、本件補正発明は、「第1ドーピング工程」と「ゲート絶縁膜形成工程」の順序について何ら特定していないものである。

また、本件補正明細書における実施例としては、「第1ドーピング工程」に対応する「n+イオンをドーピングする工程」を行った後で、「ゲート絶縁膜形成工程」に対応する「ゲート絶縁膜116」の形成工程を行う工程順序が記載されているが(甲4【0033】【0034】)、本件補正明細書全体の記載をみても、当該工程順序に限定すべきとの記載や当該工程順序とすることに技術的意義があるとの記載はない。

さらに、本件補正明細書における実施例の図10F及び図11Fでは、ゲート絶縁膜の形成工程後に、nーイオンのドーピング工程を行うことが示されているから、本件補正明細書において、「ゲート絶縁膜形成工程」の後にn型不純物(nイオン)のドーピング工程を行う方法が排除されているとはいえない。

(2) また、「ゲート絶縁膜形成工程」と「n+ オンをドーピングする工程」を含む製造方法において、これらの工程の工程順序を交換して実施できることは、次のとおり、半導体装置の技術分野において周知である。

ア 引用例1(【0307】)では、実施例8における製造方法の工程順序を、表7に記載された複数の工程順序のいずれかに変更できることが記載されている。

そして、表7の「C/D」はチャネルドープ工程を、「N+」は高濃度第一導電型不純物導入工程を、「G」はゲート電極形成工程をそれぞれ表すものであるが(【0284】)、同段落には、上記複数の工程順序に変更するための条件として、ゲート電極15、25、35及び上層側電極45を形成する工程(すなわち「G」工程)の前に、高濃度第一導電型不純物導入工程(すなわち「N+」工程)を行うことが示されている。

ここで,表 7において,例えば「5-02」と「5-14」の工程順序に注目すると,いずれも「G」工程の前に「N+」工程を行うという条件を満たしているから,「C/D」(チャネルドープ工程)と「N+」(高濃度第一導電型不純物導入工程)は工程順序を入れ替えることができるものであることがわかる。

したがって、引用例1の実施例8において、「C/D」(チャネルドープ工程)と「N+」(高濃度第一導電型不純物導入工程)とは、工程順序を交換して実施できるものである。

イ 次に、引用例1の表7では、「ゲート絶縁膜形成工程」をどの順序で行うかについては記載がないが、実施例8においては、「ゲート絶縁膜形成工程」を「チャネルドープ工程」の直前の工程として行うことが記載されている(【0288】 【0289】)。

また、他の実施例においても、図4 (a)、図5 (a)、図9 (a)、図10 (a)、図11 (a)、図13 (a)、図15 (a)等に記載されているように、「ゲート絶縁膜形成工程」と「チャネルドープ工程」は連続して行う一連の工程とされている。

このように、引用例1では、「ゲート絶縁膜形成工程」と「チャネルドープ工程」は、連続して実施する一連の工程とされているから、表7の「C/D」(チャネルドープ工程)についても、これが行われる前の段階で「ゲート絶縁膜形成工

程」が行われていることが示されているものということができる。

ウ 前記アのとおり、引用例1において、「チャネルドープ工程」と「高濃度第一導電型不純物導入工程」は工程順序を交換して実施することができるものである。 また、前記イのとおり、引用例1では、「チャネルドープ工程」が行われる前の段階で「ゲート絶縁膜形成工程」が行われることが示されている。

そして,「高濃度第一導電型不純物導入工程」は、当該工程において不純物を注入する際に必要であるマスクを形成するためのマスク形成工程も付随して行われるものであるから、本件補正発明の「第1ドーピング工程」に対応するものである。

そうすると、引用例1には、「ゲート絶縁膜形成工程」と「第1ドーピング工程」は工程順序を交換して実施可能であることが記載されているものと認められる。

エ したがって、以上のような周知事項に鑑みても、本件補正発明における「第 1ドーピング工程」と「ゲート絶縁膜形成工程」とが、工程順序の交換可能な工程 であることは、当業者にとって明らかである。

(3) 以上のとおり、本件補正発明は、「第1ドーピング工程」と「ゲート絶縁 膜形成工程」の工程順序を限定するものではなく、「ゲート絶縁膜形成工程」の後で「第1ドーピング工程」を行う方法をも含むものである。

よって、本件審決による一致点の認定に誤りはない。

- 2 相違点5の判断の誤りについて

- (1) 本件補正発明は、アレイ基板の製造に必要とされる全ての工程を漏れなく 特定したものではなく、「チャネルドープ工程」については何も特定していないの であるから、本件審決では、そもそも、引用発明の「チャネルドープ工程」につい て本件補正発明と対比・判断する必要がなかったものである。

したがって、相違点5に係る原告の主張は、本件審決の取消事由となり得るものではなく、失当である。

(2) また、次のとおり、「チャネルドープ工程」に関する本件審決の判断にも誤りはない。

ア チャネルドープ工程は、MOSトランジスタが形成される半導体基板や半導体薄膜において、関値電圧の調整のために行われるものであるから(引用例1【0006】等)、関値電圧の調整の要否に応じて、チャネルドープ工程を実施又は不実施とする場合があることは、当業者において自明である。

イ また、乙1(【0030】~【0034】)には、液晶表示装置の基板の作成方法において、チャネルドープ工程を行わない実施例が記載されているように、アクティブマトリクス回路を用いた液晶表示装置の基板について、各TFTを構成するシリコン膜に対してチャネルドープを行わずに製造することは、従来から普通に行われていることである。

ウ さらに、引用例1(【0149】【0150】)にも、アクティブマトリクス回路を用いた液晶表示装置の基板について、各薄膜トランジスタを構成するシリコン膜に対してチャネルドープを行わずに製造することが、従来から普通に行われていることが記載されている。なお、引用例1(【0150】)は、実施例1及び2において、チャネル部のシリコン膜をCVD法で形成する際に不純物ガス( $B_2$  H<sub>6</sub>)を成膜ガスに混ぜることによって所定の不純物濃度とする工程を採用する場合には、チャネル部の不純物濃度を設定するために低濃度第二導電型の不純物を打ち込む工程が不要となることを示すものである。

エ 以上のとおり、不純物が既にドープされたものとして成膜がなされている場合など、閾値電圧の調整が不要であるならば、「チャネルドープ工程」が不要であることは当業者に明らかであるから、引用発明の「チャネルドープ工程」が必須の工程ではないことは当業者にとって明らかである。

また、本件補正発明において、チャネルドープ工程を省略することにより、イオン注入によるチャネル部の結晶の乱れを抑制することができ、移動度低下を防止できるという効果は、当業者にとって自明な効果であるか、当業者であれば容易に予測し得た程度のものである。

(3) よって、相違点5に係る本件審決の判断に誤りはない。

### 第4 当裁判所の判断

- 1 本件補正発明について

- (1) 本件補正発明は、前記第2の2(2)に記載のとおりであるところ、本件補正明細書(甲4~7)には、概略、次のような記載がある。

### ア 技術分野

本発明は、液晶表示装置に係り、特に、駆動回路一体型の液晶表示装置用アレイ 基板の製造方法に関するものである(甲5【0001】)。

### イ 発明が解決しようとする課題

従来の駆動回路一体型の液晶表示装置は、カラーフィルター基板にブラックマトリックスを設計するとき、アライメント誤差を考慮したマージンを補って設計するために、開口率が低下するという問題点があった。また、半導体層と交差する部分でゲート電極が断線する不良が発生するという問題点があった(甲4【0020】)。

本発明は、そのような課題を解決するためになされたもので、その目的は、ゲート電極と半導体層が交差する部分で、ゲート電極に突出パターンを形成して、ゲート電極が断線する不良を防ぐことができ、また、薄膜トランジスタとストレージキャパシターを形成するためのドーピング工程を同時に行って工程を単純化することができ、さらに、光遮断手段をアレイ基板に形成して液晶表示装置の開口率を改善することができる液晶表示装置用アレイ基板の製造方法を得るものである(甲5【0021】)。

#### ウ 課題を解決するための手段

本発明に係る液晶表示装置用アレイ基板の製造方法は、基板の非表示領域に、アクティブ領域及びアクティブ領域の両側面のオーミックコンタクト領域が定義された第1半導体層、並びにアクティブ領域、アクティブ領域の両側面の低ドーピング領域及び低ドーピング領域の両外側面のオーミックコンタクト領域が定義された第2半導体層を形成するとともに、基板の表示領域に、アクティブ領域、アクティブ

領域の両側面の低ドーピング領域及び低ドーピング領域の両外側面のオーミックコ ンタクト領域が定義された第3半導体層並びに第4半導体層を形成する工程と;第 1半導体層全部と第2及び第3半導体層のアクティブ領域と低濃度ドーピング領域 を覆い第2及び第3半導体層のオーミックコンタクト領域及び第4半導体層全部を 露出させる第1フォトレジストパターンをドーピングマスクとして、第2半導体層 及び第3半導体層のオーミックコンタクト領域、並びに第4半導体層を高濃度n型 の不純物でドーピングする第1ドーピング工程と、第1フォトレジストパターンを 除去する工程と,第1半導体層,第2半導体層,第3半導体層,及び第4半導体層 が形成された基板上に、ゲート絶縁膜を形成する工程と、ゲート絶縁膜上に、第1 半導体層、第2半導体層及び第3半導体層のアクティブ領域に各々対応する第1ゲ ート電極, 第2ゲート電極及び第3ゲート電極, 並びに前記第4半導体層に対応す るストレージ電極を形成するとともに、表示領域に、ゲート配線を形成する工程と、 第1半導体層全部を露出させて第2ないし第4半導体層全部を覆う第2フォトレジ ストパターン及び第1ゲート電極をドーピングマスクとして、第1半導体層のオー ミックコンタクト領域に高濃度p型の不純物をドーピングする第2ドーピング工程 と、第2フォトレジストパターンを除去する工程と、第1ゲート電極、第2ゲート 電極、第3ゲート電極及びストレージ電極をドーピングマスクとして、第2半導体 層,及び第3半導体層の低ドーピング領域に低濃度n型の不純物をドーピングする 第3ドーピング工程と、第1ゲート電極、第2ゲート電極、第3ゲート電極、及び ストレージ電極、並びにゲート配線が形成された基板上に、第1半導体層を露出さ せる第1コンタクトホール及び第2コンタクトホール、第2半導体層を露出させる 第3コンタクトホール,及び第4コンタクトホール,並びに第3半導体層を露出さ せる第5コンタクトホール,及び第6コンタクトホールを含む層間絶縁膜を形成す る工程と、層間絶縁膜上に、第1コンタクトホール、及び第2コンタクトホールを 通じて第1半導体層と各々接触する第1ソース電極及び第1ドレイン電極, 第3コ ンタクトホール,及び第4コンタクトホールを通じて第2半導体層と各々接触する

第2ソース電極及び第2ドレイン電極,第5コンタクトホール,及び第6コンタクトホールを通じて第3半導体層と各々接触する第3ソース電極及び第3ドレイン電極,並びに表示領域に画素領域を定義し、ゲート配線と交差するデータ配線を形成する工程と、第1ソース電極、第2ソース電極、及び第3ソース電極、第1ドレイン電極、第2ドレイン電極、及び第3ドレイン電極並びにデータ配線が形成された基板上に、第3ドレイン電極を露出させるドレインコンタクトホールを含む保護層を形成する工程と、保護層上に、ドレインコンタクトホールを通じて第3ドレイン電極と接触するように画素領域に位置する画素電極を形成する工程とでなることを特徴とする(甲7【0023】)。

### エ 発明の効果

本発明に係る液晶表示装置用アレイ基板の製造方法は、ゲート電極を形成するとき、下部の半導体層(アクティブ層)と交差する段差部分で突出部を形成することによって、交差部分でゲート電極の断線を防ぐことができ、製造工程を単純化することができる。また、光遮断手段をアレイ基板に形成し、光遮断手段を設計するとき、アライメントマージンを考慮する必要がなくなることによって、開口率を改善することができ、高輝度を達成することができる(甲5【0024】)。

### オ 発明を実施するための最良の形態

本発明の実施の形態に係る駆動回路一体型の液晶表示装置用アレイ基板の製造方法を説明する(甲4(以下同じ)【0029】)。

図10Aないし」は、本発明の実施の形態に係る液晶表示装置用アレイ基板の製造方法における非表示領域の各工程を示す断面図であり、図11Aないし」は、本発明の実施の形態に係る液晶表示装置用アレイ基板の製造方法における表示領域の各工程を示す断面図である(【0030】)。

図10Aと図11Aは、第1マスク工程を示す断面図である。図10Aと図11 Aに示したように、第1基板100に、表示領域D1と非表示領域D2を定義し、表示領域D1には、多数の画素領域Pを定義する。この時、非表示領域D2に、第 1領域A1と第2領域A2を定義し、画素領域Pに、第3領域A3と第4領域A4を定義する。第1ないし第4領域A1、A2、A3、A4が定義された第1基板100の一面に、クロムCrのような光の反射率が低い金属を蒸着して、第1マスク工程によってパターニングし、非表示領域D2と、表示領域D1の第3領域A3及び第4領域A4と、画素領域Pの枠に対応してブラックマトリックス102を形成する。ブラックマトリックス102を形成する工程と同時に、非表示領域D2の周辺に対応する第1基板100の端に、アライメントキー(図7のAK)を形成する(【0031】)。

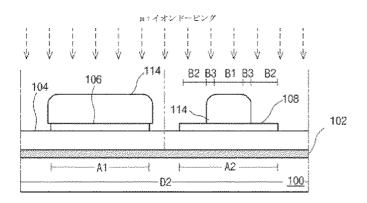

図10Bと図11Bは、第2マスク工程を示す断面図である。図10Bと図11 Bに示したように、ブラックマトリックス102が形成された第1基板100に、 絶縁物質を蒸着してバッファ層104を形成し、バッファ層104の上部に非晶質 シリコンを蒸着した後、結晶化する工程を行う。非晶質シリコンの結晶化には、一 般的に、レーザーが利用される。結晶化工程によって結晶化された層をパターニン グし、第1領域A1と第2領域A2と第3領域A3に、アクティブ層として機能す る第1ないし第3半導体層106,108,110を形成し,第4領域A4に,第 1ストレージ電極として機能する第4半導体層112を形成する(【0032】)。 図10Cと図11Cは、第3マスク工程を示す断面図である。図10Cと図11 Cに示したように、第1ないし第4半導体層106、108、110、112が形 成された第1基板100全面にフォトレジストを塗布した後、第3マスク工程によ ってパターニングし、第2領域A2及び第3領域A3の一部と第1領域A1を遮蔽 する第1フォトレジストパターン114を形成する。この時,第2領域A2と第3 領域A3に、アクティブ領域B1と、アクティブ領域B1の両側面の低ドーピング 領域B3(LDD)と、前記低ドーピング領域B3の両外側面のオーミックコンタ クト領域B2を定義する。第1フォトレジストパターン114は、特に、第2領域 A2と第3領域A3に構成された第2半導体層108と第3半導体層110のアク ティブ領域B1と低ドーピング領域B3を遮蔽するように形成する。第1フォトレ

ジストパターン114が形成された第1基板100全面に、n+イオンをドーピングする工程を行う。第2領域A2と第3領域A3のオーミックコンタクト領域B2は、<math>n+イオンがドーピングされ、第4領域A4の第4半導体層112は、第1ストレージ電極としての機能を果たす。第2領域A2及び第3領域A3の第2半導体層108及び第3半導体層110と、前記第4領域A4の第4半導体層112に、イオンをドーピングする工程が完了すると、第1フォトレジストパターン114を除去する工程を行う(【0033】)。

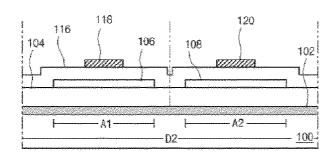

図10Dと図11Dは、第4マスク工程を示す断面図である。図10Dと図11 Dに示したように、第3マスク工程を行った後、第1基板100全面にゲート絶縁 膜116を形成する。ゲート絶縁膜116は、窒化シリコンSiN、と酸化シリコ ンSiO₂を含む無機絶縁物質グループのうちから選択された1つ以上の物質を蒸 着して形成する。ゲート絶縁膜116が形成された第1基板100全面に導電性金 属を蒸着して、第4マスク工程によってパターニングし、第1ないし第3半導体層 106,108,110の中心,すなわち,アクティブ領域B1に対応する上部に 第1ないし第3ゲート電極118,120,122を形成して,第4領域A4の第 4半導体層112に対応する上部に第2ストレージ電極124を形成すると同時に, 第3領域A3のゲート電極122から画素領域Pの一側に延長されたゲート配線1 25を形成する(図7)。ゲート電極118,120,122を形成する時、下部 の半導体層106,108,110と交差する部分に,突出部(図8BのG)を形成 することを特徴とする。半導体層106、108、110の端側に沿ってゲート電 極118,120,122から延長された突出部を形成する。この場合、交差部分 の突出部Gによってエッチング液の浸透を防ぐことができるために、ゲート電極1 18,120,122がオーバーエッチングされ断線するという不良を防ぐことが できる長所がある(【0034】)。

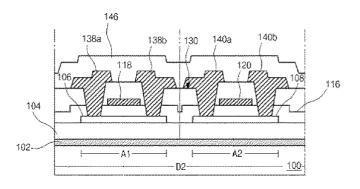

図10Hと図11Hは,第7マスク工程を示す断面図である。…前述した第1ないし第7マスク工程によって、非表示領域D2には、p型の多結晶薄膜トランジス

タと n型の多結晶薄膜トランジスタの組み合わせである CMOS素子が形成され、表示領域D1の第 3 領域A3には、n型の多結晶薄膜トランジスタが形成され、第 4 領域A4には、第 1 ストレージ電極 112 と第 2 ストレージ電極 124 で構成されたストレージキャパシターCst が形成される(【 0038】)。

前述した各工程によって、本発明の実施の形態に係る駆動回路一体型の液晶表示装置用アレイ基板を製作することができる。この時、光遮断手段102をアレイ基板に直接形成するために、従来とは異なり、アライメントマージンを考慮する必要がない。また、光遮断手段102と共にアライメントキーAKを形成したため、これを利用した正確なアライメントが可能であり、従来とは異なり、n型の多結晶薄膜トランジスタとストレージキャパシターCstを形成するためのn+ドーピング工程を同時に行うことができ、製造方法を単純化することができる長所がある。さらに、ゲート電極を形成するとき、下部の半導体層と交差する段差部分に突出部Gを形成することによって、交差部分でゲート電極が断線されるという不良を防ぐことができる長所がある(【0041】)。

(2) 以上のとおり、本件補正明細書には、駆動回路一体型の液晶表示装置用アレイ基板の製造方法に関し、従来の駆動回路一体型の液晶表示装置には、カラーフィルター基板にブラックマトリックスを設計するとき、アライメント誤差を考慮したマージンを補って設計するために開口率が低下することや、半導体層と交差する部分でゲート電極が断線する不良が発生するという問題点があったことから、かかる課題を解決するため、ゲート電極と半導体層が交差する部分で、ゲート電極に突出パターンを形成して、ゲート電極が断線する不良を防ぐこと、薄膜トランジスタとストレージキャパシターを形成するためのドーピング工程を同時に行って工程を単純化すること、さらに、光遮断手段をアレイ基板に形成して液晶表示装置の開口率を改善することができる液晶表示装置用アレイ基板及びその製造方法を得ることを目的として、本件補正発明に係る構成を採用すると、ゲート電極を形成するとき、下部の半導体層(アクティブ層)と交差する段差部分で突出部を形成することによ

って、交差部分でゲート電極の断線を防ぐことができ、製造過程を単純化すること ができ、また、光遮断手段をアレイ基板に形成し、光遮断手段を設計するとき、ア ライメントマージンを考慮する必要がなくなることによって、開口率を改善するこ とができ、高輝度を達成することができるという作用効果を奏する旨の記載がある。 もっとも、本件補正発明にあっては、「前記第1半導体層全部と前記第2及び第 3半導体層のアクティブ領域と低濃度ドーピング領域を覆い前記第2及び第3半導 体層のオーミックコンタクト領域及び前記第4半導体層全部を露出させる第1フォ トレジストパターンをドーピングマスクとして、前記第2半導体層及び第3半導体 層のオーミックコンタクト領域,並びに前記第4半導体層を高濃度n型の不純物で ドーピングする第1ドーピング工程」との構成を備えているから、薄膜トランジス タとストレージキャパシターを形成するためのドーピング工程を同時に行うもので あることは認められるものの, 光遮断手段をアレイ基板に直接形成するとの構成, 光遮断手段と共にアライメントキーを形成するとの構成、ゲート電極を形成すると き、下部の半導体層と交差する段差部分に突出部を形成するとの構成は、いずれも 備えていないから、本件補正発明が本件補正明細書に記載された上記のような作用 効果を全て奏するものではない。

### 2 引用発明について

(1) 引用発明は、前記第2の3(2)アに記載のとおりであるところ、引用例1 (甲1) には、引用発明について、概略、次のような記載がある。

### ア 発明の属する技術分野

本発明は異なる導電型薄膜トランジスタ(TFT)やTFTと容量素子とを備えるアクティブマトリクス基板等の半導体装置及びその製造方法に関するものである。 更に詳しくはこれら半導体装置の製造工程を簡略化しながら、TFTの電気的特性を最適化するための技術に関するものである(【0001】)。

### イ 従来の技術

従来、アクティブマトリクス基板 1'' は、図 3 3 (a) に示すように、絶縁基板

2の表面に形成した島状のシリコン膜10a, 20a, 30a, 40aに対して、ゲート絶縁膜14, 24, 34及び誘電体膜44を形成した後、約 $1\times10^{12}$ cm  $^{-2}$ のドーズ量でボロンイオンを打ち込む。チャネルドープを行うためである。その結果、各シリコン膜10a, 20a, 30a, 40aは低濃度P型となる。これは薄膜トランジスタの閾値電圧(Vth)を調整するために行われる(これを「CD」と省略することもある。)(【0005】【0006】)。

#### ウ 発明が解決しようとする課題

アクティブマトリクス基板の製造コストはマスク形成工程の数と、不純物導入工程の数とに大きく支配されるため、従来のようにTFTの最適化を図ろうとすると製造工程数が大幅に増えてしまうという問題点がある。例えば、LDD TFTにてCMOS構成を成し、保持容量40″も形成する場合には、ドナー又はアクセプター不純物を半導体膜に添加するためだけに5回のマスク形成工程と6回の不純物導入工程とが必要になっている。そのため、アクティブマトリクス基板の製造コストが著しく増大するとの問題点が認められる。この問題点はアクティブマトリクス基板に限らず、導電型の異なるTFTを有するその他の半導体装置やTFTと容量素子の双方を有するその他の半導体装置でも同様に存在する(【0012】)。

以上の問題点に鑑みて、本発明の課題は駆動回路内蔵のアクティブマトリクス基板の様に少なくともTFTとこのTFTと導電型の異なるTFT、あるいは容量素子を備えた半導体装置において、最小限の製造工程数によって各TFTの電気的特性を向上させた半導体装置とその製造方法及びアクティブマトリクス基板を提供することにある(【0013】)。

#### エ 課題を解決するため手段

上記課題を解決するため、本発明では半導体装置を以下の様に構成する。以下に 説明する各発明はいずれも最小限の製造工程数によって、各TFTの電気的特性を 向上させた半導体装置やその製造方法を共通の目的と課題とするが、それらを更に 分類すれば、請求項1ないし26に係る発明と請求項27ないし48に係る発明と に大別される(【0014】)。

請求項1ないし26に係る発明は、同一基板上に第一導電型及び第二導電型のTFTを有する半導体装置及びそれを適応した液晶表示装置用等のアクティブマトリクス基板に関する発明である。請求項8ないし11と請求項19ないし22は、これらの半導体装置の製造方法に関する発明である(【0015】)。

これに対して、請求項27ないし39に係る発明は同一基板上にTFTと容量素子を有する半導体装置及びそれを適応した液晶表示装置用等のアクティブマトリクス基板に関する発明である。請求項40ないし48に係る発明はこれらの半導体装置の製造方法に関する発明である(【0016】)。

### オ 発明の実施の形態

(ア) 図面を参照して本発明の実施例を説明する。なお,以下に説明するいずれの実施例も本発明に係る半導体装置を液晶表示装置における駆動回路内蔵型のアクティブマトリクス基板に適用した例で説明する。ただし,本発明の半導体装置はアクティブマトリクス基板の他にもLSIやセラミック基板上に構成された半導体装置にも適用できる。また,以下に説明するいずれのアクティブマトリクス基板もTFT等の基本的な構造が図29に示したアクティブマトリクス基板とほぼ同じであるため,以下の説明では対応する機能を有する部分には同じ符号を付してある。また,本例では第一導電型をN型とし,第二導電型をP型として説明してあるが,第一導電型をP型とし,第二導電型をN型としても良い(【0079】)。

各実施例はいずれも最小限の製造工程数によって、各TFTの電気的特性を向上させた半導体装置とその製造方法を開示するものであるが、それらを分類すると、 実施例1ないし2のグループと実施例3ないし16のグループに大別できる(【0080】)。

実施例1ないし2は、請求項1ないし26に係る発明に対応する。すなわち、同一基板上に第一導電型及び第二導電型のTFTを有する構成をベースとしている。 これに対し、実施例3ないし16は請求項27ないし48に係る発明に対応する。 すなわち、同一基板上にTFTと容量素子とを有する構成をベースとしている (【0081】)。

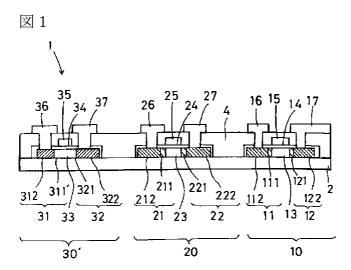

#### (イ) 実施例1

図1は、本発明に係る半導体装置を液晶表示装置における駆動回路内蔵型のアクティブマトリクス基板に適用したときの構造を模式的に示す断面図である(【0082】)。

図1において、アクティブマトリクス基板1の基体たる絶縁基板2の表面側には3つタイプのTFTが形成され、その内、右側に表されているのは第一導電型の画素用TFT10(第一導電型TFT)であり、中央に表されているのは第一導電型の駆動回路用TFT20(第一導電型TFT)であり、左側に表されているのは第二導電型の駆動回路用TFT30′(第二導電型TFT)である。これらのTFTのうち、第一導電型の駆動回路用TFT20と第二導電型の駆動回路用TFT30′は、CMOS回路として駆動回路のインバータなどを構成している。すなわち、図1に示すアクティブマトリクス基板1は、第一導電型のTFTと第二導電型のTFTとを有する半導体装置となっている(【0083】)。

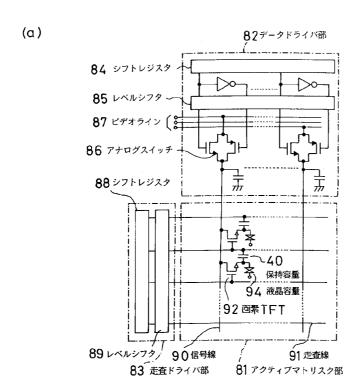

図2(a)に示すように、液晶表示装置は、そのアクティブマトリクス基板上に信号線90及び走査線91で区画形成された画素領域を有し、そこには、画素用TFT92を介して画像信号が入力される液晶セルの液晶容量94が存在する。また、信号線90に対しては、シフトレジスタ84、レベルシフタ85、ビデオライン87、アナログスイッチ86を備えるデータドライバ部82がアクティブマトリクス基板上に形成されている。走査線91に対しては、シフトレジスタ88及びレベルシフタ89を備える走査ドライバ部83がアクティブマトリクス基板上に形成されている。なお、画素領域には前段の走査線との間に保持容量40も形成されている。ここで、駆動回路用のTFTは、シフトレジスタをはじめ、レベルシフタやアナログスイッチなどに用いられているが、シフトレジスタを例に説明する。シフトレジスタ84、88では、図2(b)に2段のインバータを示すように、第一導電型

のTFTn1, n2と, 第二導電型のTFTp1, p2とによって, それぞれCMOS回路が構成されている。これらのTFTのうち, 第一導電型のTFTn1, n2は, 図1に示す第一導電型の駆動回路用TFT20に対応し, 第二導電型のTFTp1, p2は, 図1に示す第二導電型の駆動回路用TFT30′に対応し, 画素用TFT92は, 図1に示す第一導電型の画素用TFT10に対応する(【0084】)。

なお、第一導電型の画素用TFT10及び第一導電型の駆動回路用TFT20のソース・ドレイン領域11,12,21,22において、第一導電型の低濃度ソース・ドレイン領域111,121,211,221を除く領域は不純物濃度が約5×10<sup>19</sup> c m<sup>-3</sup>から約5×10<sup>20</sup> c m<sup>-3</sup>程度の第一導電型の高濃度ソース・ドレイン領域112,122,212,222であり、これらの高濃度領域に対して、各TFTに対する信号線や画素電極などのソース・ドレイン電極16,17,26,27が、層間絶縁膜4のコンタクトホールを介して電気的に接続している(【0094】)。

また,第二導電型の駆動回路用TFT30′のソース・ドレイン領域31,32において,オフセット領域311′,321′に隣接する部分は不純物濃度が約5×10<sup>19</sup> c m<sup>-3</sup>から約5×10<sup>20</sup> c m<sup>-3</sup>程度の第二導電型の高濃度ソース・ドレイン領域312,322であり,これらの高濃度領域に対して,信号線や画素電極などのソース・ドレイン電極36,37が層間絶縁膜4のコンタクトホールを介して電気的に接続している(【0095】)。

# (ウ) 実施例3

図7は、本例の液晶表示装置における駆動回路内蔵型のアクティブマトリクス基板の構造を模式的に示す断面図、図8は、液晶表示装置の構成を模式的に示すブロック図である(【0157】)。

図7において,本例の液晶表示装置の駆動回路内蔵型のアクティブマトリクス基板では,その左側領域から右側領域に向かって駆動回路部,画素領域及びこの画素

領域内の保持容量形成領域を模式的に示すように、第二導電型の駆動回路用TFT 30、第一導電型の駆動回路用TFT 20、第一導電型の画素用TFT 10及び保持容量40が同一の絶縁基板2の上に形成されている(【0158】)。

本例では、図8に示すように、画素領域には前段の走査線91との間に保持容量40が形成され、この保持容量40は液晶セル(液晶容量94)での電荷の保持特性を高める機能を有している。この保持容量40は、画素用TFT10を形成するためのシリコン膜S1と同時形成されたシリコン膜S2を導電化したものを下層側電極部40c(第一の電極部)とし、この下層側電極部40cに対して前段の走査線91から張り出した上層側電極部45(第二の電極部)が重なった状態にある。

なお、保持容量40は、各画素領域において前段の走査線91との間に構成されているが、専用の容量線との間に構成される場合もある(【0159】)。

#### (工) 実施例7

図14は、本例の液晶表示装置における駆動回路内蔵型のアクティブマトリクス 基板の構造を模式的に示す断面図である(【0262】)。

図14において、本例の液晶表示装置の駆動回路内蔵型のアクティブマトリクス基板1では、第一導電型の画素用TFT10、第一導電型の駆動回路用TFT20及び第二導電型の駆動回路用TFT30は、いずれもLDD構造を有し、いずれのTFTにおいても、チャネル領域13、23、33は、低濃度のボロンイオンによってチャネルドープしてあるため、不純物濃度が約 $1 \times 10^{17} \, \mathrm{cm}^{-3}$ の低濃度第二導電型領域である(【0263】)。

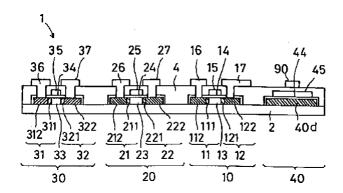

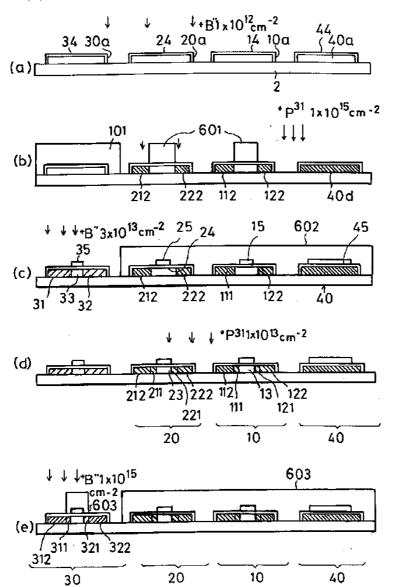

なお、別紙 2 の表 7 において、チャネルドープ工程を「C/D」、低濃度第一導電型不純物導入工程を「N $^-$ 」、高濃度第一導電型不純物導入工程を「N $^+$ 」、

低濃度第二導電型不純物導入工程を「 $P^-$ 」,高濃度第二導電型不純物導入工程を「 $P^+$ 」,ゲート電極形成工程を「G」で略して工程順序を示すように,ゲート電極15, 25, 35及び上層側電極45を形成する前に,高濃度ソース・ドレイン領域112, 122, 212, 222を形成するための高濃度第一導電型不純物導入工程を行い,この工程を援用して,下層側電極部40 dを形成するのであれば,いずれの工程順序であってもよい( $\mathbf{10284}$ )。

#### (才) 実施例8

本例のアクティブマトリクス基板の構造については実施例7と同じく図14を参照して説明する(【0286】)。

図14において、本例のアクティブマトリクス基板1の特徴点は、実施例7に係る製造方法に比してマスク形成工程が1回少ない点にあり、その製造方法は以下に説明するとおりである(【0287】)。

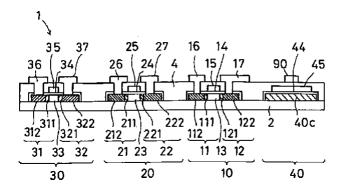

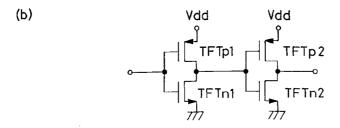

まず,図16(a)に示すように,絶縁基板2の表面に島状のシリコン膜10a, 20a,30a,40aを形成した後(シリコン膜形成工程),ゲート絶縁膜14, 24,34,及び誘電体膜44を形成する(ゲート絶縁膜形成工程)(【028 8】)。

次に、約 $1 \times 10^{12}$  c m $^{-2}$ のドーズ量でボロンイオン(第二導電型不純物/第二導電型不純物)を打ち込んでチャネルドープを行なう(チャネルドープ工程/1回目の不純物導入工程)(【0289】)。

次に、図16(b)に示すように、第二導電型の駆動回路用TFT30の形成領域を覆うと共に、後に形成するゲート電極15,25の形成予定領域を広めに覆うレジストマスク601を形成する(1回目のマスク形成工程)(【0290】)。

続いて、例えばリンイオン(第一導電型不純物/第一導電型不純物)を約 $1 \times 1$ 0 $^{15}$ cm $^{-2}$ のドーズ量でイオン注入する(2回目の不純物導入工程/高濃度第一導電型不純物導入工程)(【0291】)。

その結果、低濃度第二導電型のシリコン膜10a, 20aのうち、リンイオンが

打ち込まれた領域は,導電型が反転して不純物濃度が約 $1 \times 10^{20}$  c m $^{-3}$ の高濃度ソース・ドレイン領域112, 122, 212, 222となる。また,低濃度第二導電型のシリコン膜40 a も,導電型が反転して不純物濃度が約 $1 \times 10^{20}$  c m $^{-3}$ の高濃度第一導電型の下層側電極部40 d となる。しかる後に,レジストマスク601を除去する(【0292】)。

次に、図16(c)に示すように、ゲート電極15,25,35及び上層側電極部45を形成する(ゲート電極形成工程)。この様にして保持容量40を形成する(【0293】)。

次に、第一導電型の画素用TFT10、第一導電型の駆動回路用TFT20及び保持容量40の形成領域を覆うレジストマスク602を形成する(2回目のマスク形成工程)(【0294】)。

続いて、ボロンイオンを約 $3 \times 10^{13}$  c m $^{-2}$ のドーズ量でイオン注入する(3回目の不純物導入工程/低濃度第二導電型不純物導入工程)(【0295】)。

その結果、低濃度第二導電型のシリコン膜 30 a には、ゲート電極 35 に対して自己整合的に不純物濃度が約  $3.1 \times 10^{18}$  c m $^{-3}$  の低濃度第二導電型のソース・ドレイン領域 31 、32 が形成される。なお、不純物が導入されなかった部分がチャネル領域 33 となる。しかる後に、レジストマスク 602 を除去する(【02 96】)。

次に、図16 (d) に示す様に、レジストマスクを形成することなく、リンイオンを約 $1 \times 10^{13}$  c m $^{-2}$ のドーズ量でイオン注入する(4回目の不純物導入工程/低濃度第一導電型不純物導入工程)(【0297】)。

素用TFT10及び第一導電型の駆動回路用TFT20を形成する(【029 8】)。

ここで,低濃度第二導電型のソース・ドレイン領域 31 , 32 にも,リンイオンが  $1 \times 10^{13}$  c m<sup>-2</sup>のドーズ量でイオン注入されるが,この低濃度第二導電型のソース・ドレイン領域 31 , 32 の不純物濃度は,約  $3.1 \times 10^{18}$  c m<sup>-3</sup>である。したがって,低濃度第二導電型のソース・ドレイン領域 31 , 32 は,実質的にアクセプター型不純物濃度が約  $2.1 \times 10^{18}$  c m<sup>-3</sup>に低濃度化するだけであり,導電型は反転しない(【0299】)。

次に、図16(e)に示すように、第一導電型の画素用TFT10、第一導電型の駆動回路用TFT20及び保持容量40の形成領域を覆うと共に、ゲート電極35を広めに覆うレジストマスク603を形成する(3回目のマスク形成工程)(【0300】)。

続いて、ボロンイオンを約 $1 \times 10^{15}$  c m $^{-2}$ のドーズ量でイオン注入する(5回目の不純物導入工程/高濃度第二導電型不純物導入工程)(【0301】)。

その結果、低濃度第二導電型のソース・ドレイン領域 31、 32には不純物濃度が  $1 \times 10^{20}$  c m<sup>-3</sup>の高濃度ソース・ドレイン領域 312、 322 が形成される。また、低濃度第二導電型のソース・ドレイン領域 31、 32 のうち、レジストマスク 603 で覆われていた部分はそのまま不純物濃度が約  $2.1 \times 10^{18}$  c m<sup>-3</sup>の低濃度ソース・ドレイン領域 311、 321 となる(【0302】)。

このようにして、第二導電型の駆動回路用TFT30を形成する。しかる後に、 レジストマスク603を除去する(【0303】)。

以降,図14に示す様に,層間絶縁膜4を形成した後,活性化のためのアニールを行い,しかる後に,コンタクトホールを形成してソース・ドレイン電極16,17,26,27,36,37を形成すれば,レジストマスク601~603を形成するための3回のマスク形成工程と,5回の不純物導入工程によって,アクティブマトリクス基板1等の半導体装置を製造できる(【0304】)。

このように、本例のアクティブマトリクス基板1の製造方法では、図16(b)に示したように、ゲート電極15,25,35,及び上層側電極45を形成する前に、高濃度ソース・ドレイン領域112,122,212,222を形成するための高濃度第一導電型不純物導入工程を行い、この工程を援用して下層側電極部40dを形成している。したがって、従来の製造方法に比較して、マスク形成工程の数及び不純物導入工程の数を減らすことが可能である(【0305】)。

なお、実施例 7 と同様、ゲート電極 15、 25、 35 及び上層側電極 45 を形成する前に、高濃度ソース・ドレイン領域 112、 122、 212、 222 を形成するための高濃度第一導電型不純物導入工程を行い、この工程を援用して、下層側電極部 40 d を形成するのであれば、表 7 に示すいずれの工程順序であってもよい(【 0307】)。

- (2) 以上の記載からすると、引用発明は、導電型薄膜トランジスタ(TFT)等を備えるアクティブマトリクス基板等の半導体装置の製造において、そのコストは、マスク形成工程の数と不純物導入工程の数とに大きく支配されるため、従来のように薄膜トランジスタの最適化を図ろうとすると、製造工程数が大幅に増えてしまうという問題点があったことから、最小限の製造工程数によって各薄膜トランジスタの電気的特性を向上させた半導体装置とその製造方法及びアクティブマトリクス基板を提供することを目的とし、引用発明に係る構成とすることにより、マスク形成工程の数や不純物導入工程の数を減らすことができるとの作用効果を奏するというものである。

- 3 乙1について

- (1) 液晶表示装置に関する乙1には、概略、次のような記載がある。

- ア 産業上の利用分野

本明細書で開示する発明は、アクティブマトリクス型の液晶表示装置に関するものである(【0001】)。

イ 実施例1

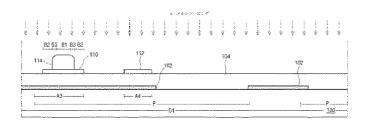

- (ア) 本発明におけるアクティブマトリクス回路を用いた液晶表示装置の基板の作製方法の説明を行う。以下、本実施例のモノリシック型アクティブマトリクス回路を得る制作工程について、図1を用いて説明する。この工程は低温ポリシリコンプロセスのものである。図1の左側に駆動回路のTFT(薄膜トランジスタ)の作製工程を、右側にアクティブマトリクス回路のTFTの作製工程をそれぞれ示す。まず、第一の絶縁基板としてガラス基板101の上に、下地酸化膜102として厚さ1000~3000名の酸化珪素膜を形成した。この酸化珪素膜の形成方法としては、酸素雰囲気中でのスパッタ法やプラズマCVD法を用いればよい(【0030】)。

- (イ) その後、プラズマCVD法やLPCVD法によってアモルファスのシリコン膜を $300\sim1500$  Å、好ましくは $500\sim1000$  Åに形成した。そして、500 ℃以上、好ましくは、 $500\sim600$  ℃の温度で熱アニールを行い、シリコン膜を結晶化させた、若しくは結晶性を高めた。熱アニールによって結晶化の後、光(レーザーなど)アニールを行って、更に結晶化を高めてもよい。また、熱アニールによる結晶化の際に、特開平6-244103 号公報、特開平6-244104 号公報に記述されているように、ニッケル等のシリコンの結晶化を促進させる元素(触媒元素)を添加してもよい(【0031】)。

- (ウ) 次に、シリコン膜をエッチングして、島上の駆動回路のTFTの活性層103(pチャネル型TFT用)、104(Nチャネル型TFT用)とマトリクス回路のTFT (画素TFT)の活性層105を形成した。さらに、酸素雰囲気中でのスパッタ法によって厚さ500~2000Åの酸化珪素のゲート絶縁膜106を形成した。ゲート絶縁膜の形成方法としては、プラズマCVD法を用いてもよい。プラズマCVD法によって酸化珪素膜を形成する場合には、原料ガスとして、一酸化二窒素( $N_2$ O)若しくは酸素( $O_2$ )とモノシラン( $SiH_4$ )を用いることが好ましかった(【0032】)。

- (エ) その後、厚さ2000~6000Åのアルミニウムをスパッタ法によって

基板全面に形成した。ここでアルミニウムはその後の熱プロセスによってヒロックが発生するのを防止するため、シリコンまたはスカンジウム、パラジウムなどを含有するものを用いてもよい。そしてこれをエッチングしてゲート電極107,108,109を形成する。(図1(A))

次に、このアルミニウムを陽極酸化する。陽極酸化によってアルミニウムの表面は酸化アルミニウム110、111、112となり、絶縁物としての効果を有する様になる。(図1(B))(【0033】)

次に、Pチャネル型T F T の活性層を覆うフォトレジストのマスク113を形成する。そしてイオンドーピング法によってフォスフィンをドーピングガスとして燐を注入する。ドーズ量は $1 \times 10^{12} \sim 5 \times 10^{13}$ 原子/c  $m^2$  とする。この結果として,強いN型領域(ソース,ドレイン)114,115が形成される。(図1 (C))

次に、Nチャネル型TFTの活性層及び画素TFTの活性層を覆うフォトレジストのマスク 1 1 6 を形成する。そして、再びイオンドーピング法によってジボラン  $(B_2H_6)$  をドーピングガスとしてホウ素を注入する。ドーズ量は $5\times10^{14}\sim8\times10^{15}$ 原子/c  $m^2$ とする。この結果として、P型領域 1 1 7 が形成される。

以上のドーピングにより、強いN型領域(ソース、ドレイン)  $1\,1\,4$ 、  $1\,1\,5$ 、 強いP型領域(ソース、ドレイン)  $1\,1\,7$  が形成される。(図1 (D))(【 $0\,0\,3\,4$ 】)

- (2) 以上の記載からすると、本件出願に係る優先権主張日当時、アクティブマトリクス回路を用いた液晶表示装置の基板の製造において、各薄膜トランジスタを構成するシリコン膜に対してチャネルドープを行わずにこれを製造することは、半導体装置製造の技術分野において、普通に行われていたことがうかがえる。

- 4 一致点の認定の誤りについて

- (1) 原告は、本件補正発明の第1ドーピング工程はゲート絶縁膜が形成されない状態で行われるのに対し、引用発明のドーピング工程はゲート絶縁膜が形成され

た後に行われるものであるとして、本件補正発明と引用発明とは、「第1ドーピン グ工程」の後に「ゲート絶縁膜を形成する工程」が行われる点で一致するとした本 件審決の認定は誤りであると主張する。

しかしながら、本件審決は、前記第2の3(2)イに記載のとおり、本件補正発明と引用発明とは、「前記第1半導体層全部と前記第2及び第3半導体層のアクティブ領域と低濃度ドーピング領域を覆い前記第2及び第3半導体層のオーミックコンタクト領域及び前記第4半導体層全部を露出させる第1フォトレジストパターンをドーピングマスクとして、前記第2半導体層及び第3半導体層のオーミックコンタクト領域、並びに前記第4半導体層を高濃度n型の不純物でドーピングする第1ドーピング工程と、」と「前記第1半導体層、第2半導体層、第3半導体層、及び第4半導体層が形成された基板上に、ゲート絶縁膜を形成する工程と、」を含む点で一致していると認定しているものの、これらの工程の順序については何ら特定していないから、原告が主張するように、本件補正発明と引用発明とが「第1ドーピング工程」の後に「ゲート絶縁膜を形成する工程」が行われる点で一致すると認定したものではない。

したがって、原告の上記主張は、その前提において誤りである。

(2) また、本件補正明細書には、「第1ドーピング工程」の後に「ゲート絶縁膜を形成する工程」を行うことの技術的意義は何ら記載されていないものの、発明の実施の形態としては、薄膜トランジスタが形成される第2及び第3半導体層(図10C)とストレージキャパシターのストレージ電極が形成される第4半導体層(【0038】図11C)に対して、ゲート絶縁膜116(図10D)が形成されない状態で第1ドーピング工程(n+ドーピング)を行い(図10C、図11C参照)、その後にゲート絶縁膜116を形成することが記載されている。

しかしながら、本件補正発明に係る特許請求の範囲の「前記第1半導体層全部と前記第2及び第3半導体層のアクティブ領域と低濃度ドーピング領域を覆い前記第2及び第3半導体層のオーミックコンタクト領域及び前記第4半導体層全部を露出

させる第1フォトレジストパターンをドーピングマスクとして,前記第2半導体層及び第3半導体層のオーミックコンタクト領域,並びに前記第4半導体層を高濃度 n型の不純物でドーピングする第1ドーピング工程と,前記第1フォトレジストパターンを除去する工程と,前記第1半導体層,第2半導体層,第3半導体層,及び第4半導体層が形成された基板上に,ゲート絶縁膜を形成する工程と,」との記載からすると,「第1ドーピング工程」の後に「前記第1フォトレジストパターンを除去する工程」が行われることは明らかであるものの,前記のような特許請求の範囲の記載が,「第1ドーピング工程」と「ゲート絶縁膜を形成する工程」との順序についても,「第1ドーピング工程」の後に「ゲート絶縁膜を形成する工程」を行うものであると特定しているとまではいい難い。

また、本件補正発明に係る特許請求の範囲では、その発明特定事項である各工程の内容が記載された上で、末尾において、「…でなることを特徴とする液晶表示装置用アレイ基板の製造方法。」と記載されているが、このような末尾の記載もそれ自体が各工程の順序を特定するものとはなっていない。

そして、アクティブマトリックス回路を用いた液晶表示装置の基板の製造において、半導体層上にゲート絶縁膜を形成し、その後にゲート絶縁膜を介して、高濃度 n型の不純物でドーピングすることは、引用例及び乙1から、本件出願に係る優先権主張日当時、当該技術分野において普通に行われていたことがうかがえ、技術常識であったと認められる。

さらに、前記1(2)のとおり、本件補正発明は、薄膜トランジスタを構成する第2半導体層及び第3半導体層のオーミックコンタクト領域並びにストレージキャパシターを構成する第4半導体層を高濃度n型の不純物でドーピングする第1ドーピング工程により、薄膜トランジスタとストレージキャパシターを形成するためのドーピング工程を同時に行うようにしたとの作用効果を奏するというものであるところ、本件出願に係る優先権主張日当時における上記の技術常識に照らせば、第2ないし第4の半導体層上にゲート絶縁膜を形成し、その後にゲート絶縁膜を介して高

濃度n型の不純物でドーピングするようにしても、上記の作用効果を奏することは、 本件補正明細書の記載に接した当業者には自明な事項であるということができる。

そうすると、本件補正発明に係る特許請求の範囲の記載や本件出願に係る優先権 主張日当時の技術常識によれば、本件補正発明は、「ゲート絶縁膜を形成する工程」の後に「第1ドーピング工程」を行う場合をも包含しているものと認めるのが 相当であり、「第1ドーピング工程」の後に「ゲート絶縁膜を形成する工程」を行 うものと限定されているということはできない。

したがって、第1ドーピング工程とゲート絶縁膜を形成する工程とを含む点で一 致するとした本件審決の認定に誤りはない。

#### (3) 原告の主張について

原告は、「ゲート絶縁膜を形成する工程」の後に「第1ドーピング工程」を行う ものである引用発明において、本件補正発明と同等のドーピング濃度及びドーピン グ深さを得るためには、ドーピング工程のために本件補正発明より大きな消費電力 が必要であり、同じ消費電力では本件補正発明と同等のドーピング濃度及びドーピ ング深さを得ることができないと主張する。

しかしながら、前記のとおり、本件補正発明において、第1ドーピング工程とゲート絶縁膜を形成する工程との順序関係は特定されているということはできないから、本件補正発明が上記の効果を奏するとは認められないし、また、前記のとおり、本件補正明細書にも、「第1ドーピング工程」の後に「ゲート絶縁膜を形成する工程」を行うことの技術的意義は何ら記載されていない。

したがって、原告の上記主張は、採用することができない。

- 5 相違点5の判断の誤りについて

- (1) 原告は、引用発明においては、図16(a)に示される「チャネルドープ 工程」は必須の工程であるから、引用発明においてチャネルドープ工程を有さない ものとすることは当業者が適宜になし得たことであるとした本件審決の判断は誤り であると主張する。

しかしながら、チャネルドープは、薄膜トランジスタの閾値電圧(Vth)を調整するために行われるものであるところ(甲1【0006】)、前記のとおり、本件出願に係る優先権主張日当時、アクティブマトリックス回路を用いた液晶表示装置の基板の製造において、各薄膜トランジスタを構成するシリコン膜に対してチャネルドープを行わずにこれを製造することは、本件出願に係る優先権主張日当時、半導体装置製造の技術分野において普通に行われていたことがうかがえる。また、本件補正明細書にも、チャネルドープを行わないことについての技術的課題や意義についての記載はない。

そうすると、チャネルドープを実施するかどうかは、薄膜トランジスタに求められる電気的特性に応じて、当業者において、適宜選択することができるものである。そして、引用発明は、前記のとおり、最小限の製造工程数によって薄膜トランジスタの電気的特性を向上させた半導体装置とその製造方法及びアクティブマトリクス基板を提供することを目的とするものであるから、引用発明についても、製造工程数をより少なくするため、「約 $1 \times 10^{12} \, \mathrm{cm}^{-2}$ のドーズ量でボロンイオン(第二導電型不純物)を打ち込んでチャネルドープを行なうチャネルドープ工程」を行わずに基板を製造することは、薄膜トランジスタに求められる電気的特性に応じて、当業者において、適宜選択することができるものというべきである。

したがって、引用発明において、「チャネルドープ工程」が必須の工程であると いうことはできない。

(2) 原告は、乙1には、チャネルドープを行わない液晶表示装置の基板の作成 方法が開示されているものの、乙1では、プラズマCVD法あるいはLPCVD法 をチャネルドープの代わりに用いる技術を開示しているにすぎず、チャネル工程を 他の工程に置き換えるだけでは、「3回のドーピング工程だけで成り立つ」という 本件補正発明の技術的意義を達成することはできないなどと主張する。

しかしながら、乙1には、プラズマCVD法やLPCVD法によってアモルファ スのシリコン膜を形成し、熱アニールによりシリコン膜を結晶化させた、又はシリ コン膜の結晶性を高めた後、シリコン膜をエッチングして、駆動回路及びマトリクス回路のTFT活性層を形成し、さらに、酸素雰囲気中でのスパッタ法やプラズマ CVD法によって酸化珪素のゲート絶縁膜を形成することが記載されているだけで、上記シリコン膜を形成する際に、プラズマCVD法あるいはLPCVD法をチャネルドープの代わりに用いることが記載されているものとは認められない。

そうすると、原告の上記主張は、乙1の記載に基づかないものであって、失当で ある。

- (3) よって、本件審決による相違点5の判断に誤りはない。

- 6 小括

以上によれば、本件補正発明の容易想到性に係る本件審決の判断に誤りはない。

なお、原告は、本願発明の容易想到性に係る本件審決の判断については、その取 消事由を何ら主張、立証していないが、本願発明の構成を全て含み、これをより限 定したものである本件補正発明が当業者において容易に想到することができたもの である以上、本願発明も、当業者において容易に想到することができたものである というべきである。

#### 第5 結論

以上の次第であるから,原告主張の取消事由は理由がなく,本件審決にこれを取り消すべき違法は認められない。

したがって,原告の請求は棄却されるべきものである。

知的財產高等裁判所第4部

裁判長裁判官 富 田 善 範

裁判官 大鷹 一郎

裁判官 齋 藤 巖

#### (別紙1)

## 本件補正明細書(甲4~7)の図面

## 図10C

## 図10D

#### 図11C

# 図10 J

## 図 1 1 J

#### (別紙2)

## 引用例1 (甲1) の図面及び表

## 図 7

#### 図 1 4

図20

図 2

表7(【0285】)

|         |     |                |            |     | e              |    |

|---------|-----|----------------|------------|-----|----------------|----|

| 工程順序    | 1   | 2              | 3          | 4   | 5              | 6  |

| 5 - 0 1 | C/D | N *            | G          | P - | N-             | P+ |

| 5-02    | c/D | N+             | G          | P-  | P+             | N- |

| 5-03    | C/D | N+             | G          | P+  | P-             | N- |

| 5-04    | C/D | N+             | P +        | G   | P-             | N- |

| 5-05    | C/D | P*             | N+         | G   | P-             | N- |

| 5-06    | P+  | C/D            | N+         | G   | $\mathbf{P}^-$ | N- |

| 5 - 0 7 | C/D | N*             | G          | N-  | P-             | P* |

| 5-08    | C/D | N+             | G          | N-  | P+             | P- |

| 5-09    | C/D | N*             | G          | P*  | N-             | P- |

| 5-10    | C/D | N*             | <b>P</b> + | G   | N-             | P- |

| 5-11    | C/D | P*             | N+         | G   | N-             | P- |

| 5 - 1 2 | P*  | C/D            | N+         | G   | N-             | P- |

| 5-13    | N+  | C/D            | G          | P-  | N-             | P* |

| 5-14    | N+  | C/D            | G          | P-  | P+             | N- |

| 5-15    | N+  | C/D            | G          | P+  | P-             | N- |

| 5-16    | N+  | C/D            | P+         | G   | P-             | N- |

| 5 - 1 7 | N+  | <b>P</b> +     | C/D        | G   | P-             | N- |

| 5 – 1 8 | P*  | N <sup>+</sup> | C/D        | G   | P-             | N- |

| 5-19    | N*  | C/D            | G          | N-  | P-             | P+ |

| 5 - 2 0 | N+  | C/D            | G          | N-  | P+             | P- |

| 5-21    | N+  | C/D            | G          | P+  | N-             | Р- |

| 5-22    | N+  | C/D            | P*         | G   | N-             | P- |

| 5-23    | N+  | P+             | C/D        | G   | N-             | P- |

| 5 – 2 4 | P*  | N+             | C/D        | G   | Ñ~             | P- |

|         |     |                |            |     |                |    |