令和4年3月28日判決言渡

令和2年(行ケ)第10146号 特許取消決定取消請求事件 口頭弁論終結日 令和4年2月2日

判

5

原 告 ビューワークス カンパニー リミテッド

同訴訟代理人弁護士 大 野 聖 二 同訴訟代理人弁理士 松 野 知 紘

10

被 告 特 許 庁 長 官 同指定代理人 中 村 則 夫 努 司 渡 辺 同 清 水 TE. 方 輔 同 木 庸 文 主

15

20

- 1 原告の請求を棄却する。

- 2 訴訟費用は原告の負担とする。

- 3 この判決に対する上告及び上告受理申立てのための付加期間を30日と定める。

事実及び理由

# 第1 請求

特許庁が異議2018-701050号事件について令和2年8月18日に した決定を取り消す。

# 25 第2 事案の概要

1 特許庁における手続の経緯等(当事者間に争いがない。)

- (1) 原告は、発明の名称を「TDIラインイメージセンサ」とする発明について、平成27年5月14日(優先日平成26年5月15日(以下「本件優先日」という。)、優先権主張国韓国)を国際出願日とする特許出願(特願2016-567850号。以下「本件出願」という。)をし、平成30年6月8日、特許権の設定登録を受けた(特許第6348992号。請求項の数1。以下、この特許を「本件特許」という。)。

- (2) 本件特許について、平成30年12月25日、株式会社レクレアルから特 許異議の申立て(異議2018-701050号事件)がされた。

- (3) 原告は、平成31年3月18日、取消理由通知を受けたため、令和元年6月24日付けで特許請求の範囲及び本件出願の願書に添付した明細書(以下「本件明細書」という。)の記載について訂正請求をしたが、同年8月29日、取消理由通知を受け、さらに同年12月4日付けで特許請求の範囲及び本件明細書の記載について訂正請求をしたが、令和2年2月7日、取消理由通知を受けたため、同年5月13日付けで特許請求の範囲及び本件明細書の記載について訂正請求(以下、この請求に係る訂正を「本件訂正」という。)をした。

その後、特許庁は、令和2年8月18日、本件訂正を認めた上で、「特許第6348992号の請求項1に係る特許を取り消す。」との決定(以下「本件決定」という。)をし(付加期間90日)、その謄本は、同年9月1日、原告に送達された。

- (4) 原告は、令和2年12月24日、本件決定の取消しを求める本件訴訟を提起した。

- 2 特許請求の範囲の記載

- (1) 本件訂正後の特許請求の範囲の請求項1の記載は、以下のとおりである (以下、本件訂正後の請求項1に係る発明を「本件発明」という。)。

## 【請求項1】

10

15

20

25

M個のCCDが一列配列されたラインセンサーと、スキャン方向に並列にN個の前記ラインセンサーが配列されて、前記ラインセンサーのコラム別に蓄積された電荷を並行方向に移動させて蓄積する画素部;および

前記画素部に蓄積された前記電荷をコラム別に並列入力を受けてAD変換して保存した後順次出力する出力部を含み、

前記出力部は、

10

15

20

25

前記画素部に蓄積された前記電荷をコラム別に電荷保存ノードに並列入力を 受けてそれぞれ増幅するためのM個の増幅器;

前記増幅器から出力される各信号をAD変換するM個のAD変換器;および 前記AD変換器の出力を保存して順次出力するメモリーバッファー;を含み 前記増幅器は、前記画素部のN個の前記ラインセンサーのうち最後のライン センサーから電荷が移動して蓄積された電荷保存ノードの電位によりターンオ ンされて電圧値を出力するソースフォロワ増幅器であり、

コラム別に、前記M個のCCDに蓄積された電荷が、前記電荷保存ノードに蓄積され、その蓄積された電荷は前記各ソースフォロワ増幅器を通じて増幅された後、前記各AD変換器を通じてAD変換されて出力され、前記コラム別に設けられたリセットゲートを通じて、前記コラム別に設けられたリセットドレインに連結された電圧に前記電荷保存ノードをリセットさせ、

前記電荷保存ノードが1つのラインセンサーの電荷の入力を受けることと、 前記電荷保存ノードをリセットさせることと、が交互に行われることを特徴と する、TDIラインイメージセンサ。

- (2) 本件決定が分説した請求項1は、以下のとおりである。

- (A) M個のCCDが一列配列されたラインセンサーと、スキャン方向に並列 にN個の前記ラインセンサーが配列されて、前記ラインセンサーのコラム別 に蓄積された電荷を並行方向に移動させて蓄積する画素部;および

- (B) 前記画素部に蓄積された前記電荷をコラム別に並列入力を受けてAD変

換して保存した後順次出力する出力部を含み、 前記出力部は、

- (C) 前記画素部に蓄積された前記電荷をコラム別に電荷保存ノードに並列入 力を受けてそれぞれ増幅するためのM個の増幅器;

- (D) 前記増幅器から出力される各信号をAD変換するM個のAD変換器; および

- (E) 前記AD変換器の出力を保存して順次出力するメモリーバッファー; を含み、

- (F) 前記増幅器は、前記画素部のN個の前記ラインセンサーのうち最後のラインセンサーから電荷が移動して蓄積された電荷保存ノードの電位によりターンオンされて電圧値を出力するソースフォロワ増幅器であり、

- (G) コラム別に、前記M個のCCDに蓄積された電荷が、前記電荷保存ノードに蓄積され、その蓄積された電荷は前記各ソースフォロワ増幅器を通じて増幅された後、前記各AD変換器を通じてAD変換されて出力され、前記コラム別に設けられたリセットゲートを通じて、前記コラム別に設けられたリセットドレインに連結された電圧に前記電荷保存ノードをリセットさせ、

- (H) 前記電荷保存ノードが1つのラインセンサーの電荷の入力を受けること と、前記電荷保存ノードをリセットさせることと、が交互に行われる

- (I) ことを特徴とする、TDIラインイメージセンサ。

- 20 3 本件決定の要旨

10

15

- (1) 本件決定が認定した本件優先日前に頒布された刊行物である米国特許第7796174号明細書(甲2。以下「甲2文献」という。)に記載された発明(以下「甲2発明」という。)、本件発明と甲2発明の一致点及び相違点は、以下のとおりである。

- 25 ア 甲2発明

- (2a) CCDイメージングセンサアレイ124は、複数のサブアレイ12

- 04に属するピクセル604を含み、

- (2b) ピクセルの各列は、センスノード804に接続し、センスノード8 04はフローティングディフュージョンへのコンタクトを有し、

- (2c) 各センスノード804には、増幅器1208が接続され、増幅器は ソースフォロアで構成され、

- (2d) 各センスノード804には、当該センスノード804をリセットするためのリセットトランジスタが接続され、当該リセットトランジスタは、 ゲートと、Vresetに接続されたダイオードドレインを有し、

- (2 e) ピクセルからの信号は、アナログデジタル変換器1220により処理され、シリアライザ1224により処理される

- (2 f) TD I イメージャ。

- イ 一致点及び相違点

#### (一致点)

10

15

20

25

- (A) M個のCCDが一列配列されたラインセンサーと、スキャン方向に並列にN個の前記ラインセンサーが配列されて、前記ラインセンサーのコラム別に蓄積された電荷を並行方向に移動させて蓄積する画素部:および

- (B) 前記画素部に蓄積された前記電荷をコラム別に並列入力を受けてAD 変換して保存した後順次出力する出力部を含み、

前記出力部は、

- (C) 前記画素部に蓄積された前記電荷をコラム別に電荷保存ノードに並列 入力を受けてそれぞれ増幅するためのM個の増幅器:

- (D) 前記増幅器から出力される各信号をAD変換するM個のAD変換器; および

- (E') 前記AD変換器の出力を保存して順次出力する手段;を含み、

- (F) 前記増幅器は、前記画素部のN個の前記ラインセンサーのうち最後の ラインセンサーから電荷が移動して蓄積された電荷保存ノードの電位に

よりターンオンされて電圧値を出力するソースフォロワ増幅器であり、

- (G) コラム別に、前記M個のCCDに蓄積された電荷が、前記電荷保存ノードに蓄積され、その蓄積された電荷は前記各ソースフォロワ増幅器を通じて増幅された後、前記各AD変換器を通じてAD変換されて出力され、前記コラム別に設けられたリセットゲートを通じて、前記コラム別に設けられたリセットドレインに連結された電圧に前記電荷保存ノードをリセットさせ、

- (H) 前記電荷保存ノードが1つのラインセンサーの電荷の入力を受けることと、前記電荷保存ノードをリセットさせることと、が交互に行われる

- (I) ことを特徴とする、TDIラインイメージセンサ。

## (相違点)

10

20

「前記AD変換器の出力を保存して順次出力する手段」が、本件発明においては「メモリーバッファー」であるのに対し、甲2発明においては「シリアライザ」である点。

5 (2) 相違点に関する本件決定の判断は以下のとおりである。

甲2発明における「シリアライザ」は、「前記AD変換器の出力を保存して順次出力する」ものであり、この動作を「メモリー」を用いて行うことができることは明らかである。

また、「メモリー」は、「メモリーバッファー」ともいえるから、相違点に 係る構成は当業者が容易に想到し得ることである。

したがって、本件発明は、甲2発明に基づいて当業者が容易に発明できた ものであるから、特許法29条2項の規定により特許を受けることができな いものであり、本件特許の請求項1に係る特許は取り消されるべきものであ る。

#### 25 第3 当事者の主張

1 原告の主張

## (1) 甲2発明の認定の誤り

10

15

20

25

本件発明は、「TDIラインイメージセンサ」であり、本件明細書の記載を 参酌すると、「TDIラインイメージセンサ」とは、「TDIラインスキャン 方式のイメージセンサ」であり(【0010】)、「ラインスキャン方式」とは 「一度に一ラインずつ任意の速度で露出および転送する方式」(【0007】) とされていることから、本件発明は、一度に一ラインずつ電荷の転送を行う ラインスキャン方式のTDIラインイメージセンサである。そして、本件発 明は、一度に一ラインずつ電荷の転送を行うために、「前記電荷保存ノードが 1つのラインセンサーの電荷の入力を受けることと、前記電荷保存ノードを リセットさせることと、が交互に行われ」るとの発明特定事項(構成要件H) を有しており、「電荷保存ノードが1つのラインセンサーの電荷の入力を受 けること」と、「電荷保存ノードをリセットさせること」との関係として、こ れらが交互に行われることが特定されているから、本件発明と対比する甲2 発明の認定においては、「ラインセンサーの電荷の入力を受けること」と、「電 荷保存ノードをリセットさせること」との関係を認定すべきである。そうす ると、甲2の第8欄58~60行には、「After being sensed(possibly multiple times), the signal charge packets can be removed through a diode drain」(訳:検知された後(おそらく複数回)、信号電荷パケットはダ イオードドレインを介して除去することができる。)との記載があり、また、 本件決定は、上記の「After being sensed(possibly multiple times)」につ いて、「possibly」が確信度が低い副詞であることを勘案すると、「検知され た後(複数回の場合もある)」という意味に理解するのが適切であると判断し ているのであるから、甲2発明は、以下のとおり認定されるべきである(下 線部が本件決定と異なる点である。)。

(2a) CCDイメージングセンサアレイ124は、複数のサブアレイ1204に属するピクセルを含み、

- (2b) ピクセルの各列は、センスノード804に接続し、センスノード804はフローティングディフュージョンへのコンタクトを有し、

- (2 c) 各センスノード804には、増幅器1208が接続され、増幅器はソースフォロアで構成され、

- (2 d) 各センスノード804には、当該センスノード804をリセットするためのリセットトランジスタが接続され、当該リセットトランジスタは、ゲートと、Vresetter

- (2 d') <u>各センスノード804に蓄積された電荷が複数回検知された後</u>に、各センスノード804の信号電荷パケットが除去される場合もあり、

- (2e) ピクセルからの信号は、アナログデジタル変換器1220により処理され、シリアライザ1224により処理される

- (2 f) TDIイメージャ。

- (2) 取消事由1 (相違点2又は2'の看過)

#### ア 相違点2

10

15

20

25

(ア) 甲2発明の「センスノード」は本件発明の「電荷保存ノード」に相当し、甲2発明において「センスノード」に「電荷」が「蓄積され」て「検知され」ることは、本件発明において「電荷保存ノード」が「1つのラインセンサーの電荷の入力を受ける」ことに相当する。そして、甲2発明において「センスノード804の信号電荷パケットが除去される」ことは、本件発明において「電荷保存ノードをリセットさせること」に相当するから、本件発明と甲2発明の相違点としては、本件決定が認定した相違点に加えて、以下の相違点2も認定されるべきである。

#### 「相違点2]

本件発明では、電荷保存ノードが1つのラインセンサーの電荷の入力を受けることと、電荷保存ノードをリセットさせることと、が交互に行われる、一度に一ラインずつ電荷の転送を行うラインスキャン方式のT

DIラインイメージセンサであるのに対し、甲2発明では、電荷保存ノードが1つのラインセンサーの電荷の入力を複数回受けた後に、電荷保存ノードをリセットさせる場合があり、一度に一ラインずつ電荷の転送を行うラインスキャン方式であるか否かが不明である点。

(イ) 「複数回受けた後に」という構成を有する甲2発明を「交互に」行うと変更する動機付けはなく、また、甲2発明におけるラインセンサーからの電荷入力を複数回受けた後にリセットを行うという動作は、複数ラインからの電荷信号を積算することを意味しており、ライン方向の解像度を犠牲にするかわりに感度を向上させるという技術思想に基づくも

のである。これに対して、本件発明は、電荷入力とリセットとを交互に 行って一度に一ラインずつ電荷の転送を行うことで感度を犠牲にしつつ

解像度を向上させるという技術思想であり(本件明細書の【0015】)、

相違点2は、本件発明の容易想到性の判断の結論に影響するものである。

#### イ 相違点2'

10

15

20

25

仮に、本件決定がした甲2発明の認定に誤りがないとしても、甲2発明は、「電荷保存ノードが1つのラインセンサーの電荷の入力を受けること」と、「電荷保存ノードをリセットさせること」との関係が不明であるから、以下のとおりの相違点2'が認定されるべきであり、この相違点2'は、本件発明の容易想到性の判断の結論に影響するものである。

#### 「相違点2']

本件発明では、電荷保存ノードが1つのラインセンサーの電荷の入力を 受けることと、電荷保存ノードをリセットさせることと、が交互に行われ るのに対し、甲2発明ではそのようになっているのか不明である点。

## ウ 被告の主張について

(ア) 被告は、後記2(1)のとおり、文献(乙2,3,5ないし7)を挙げて、「電荷保存ノード」に相当する「センスノード」が電荷を受け入れ、

センスノードに接続されたリセットトランジスタによるリセットが交互 に行われることは技術常識(以下「本件技術常識」という。)であるから、 相違点2は存しない旨主張する。

しかし、①甲2発明は、フローティングゲートアンプ(FGA:Floating Gate Amplifier。以下「FGA」と略する。)タイプであり、センスノード804に浮遊ゲート(FG)904が含まれ、②甲2発明における「センスノードをリセットさせる」とは、浮遊ゲート(FG)904を一定の電圧にすること(浮遊ゲート904のリセット)を含む、といった特徴を有するところ、特開2002-158346号公報(乙2。公開日平成14年5月31日。以下「乙2文献」という。)及び特開昭60-165760号公報(乙3。公開日昭和60年8月28日。以下「乙3文献」という。)に記載された発明は、フローティングディフュージョンアンプ(FDA:Floating Diffusion Amplifier。以下「FDA」と略する。)タイプであり、出力部の構成が甲2に記載された発明とは異なる(上記①の特徴を有しない。)。

10

15

20

25

次に、特開平7-161969号公報(乙6。公開日平成7年6月23日。以下「乙6文献」という。)には、甲2発明における「浮遊ゲート904のリセット」に対応する事項の開示はなく、また、その【図5】及び【図6】において、FG30には、甲2発明のリセットトランジスタに相当するものは接続されておらず、FG30を一定の電圧にすることの示唆はないから、乙6文献に記載された発明は、上記②の特徴を有しない。

また、FGAタイプは、出力部の浮遊拡散領域(FD: Floating Diffusion)の上に絶縁膜を介して設けた検出電極(FG)の電位を検出するものであるところ、特開 2008-60097 号公報(Z0、公開日平成 Z0年3月13日。以下「Z7文献」という。)に記載された発明

は、コントロールゲート35の電位を検出するものではなく、チャネル領域21に生じた電位変化を駆動トランジスタ31を介して信号出力をするものである(【0018】)から、FGAタイプにおけるFGに該当しないため、FGAタイプではなく、上記①の特徴を有しない。仮に、乙7文献に記載された発明がFGAタイプであるとしても、甲2発明における「浮遊ゲート904のリセット」に対応する事項の開示はないし、コントロールゲート35には、甲2発明のリセットトランジスタに相当するものは接続されておらず(乙7の図1参照)、コントロールゲート35を一定の電圧にすることの示唆すらないから、上記②の特徴を有しない。

このように、乙2文献及び乙3文献に記載された発明はFDAタイプであり、乙7文献に記載された発明もFGAタイプであるとはいえないから、これらは甲2発明に採用されている技術常識を認定する根拠になり得ず、仮にFGAタイプであるとしても、甲2発明における「浮遊ゲート904のリセット」に対応する事項の開示はなく、また、乙6文献には、甲2発明における浮遊ゲート904のリセットの開示がないから、甲2発明に採用されている技術常識を認定する根拠となり得ない。

(イ) また、仮に、本件技術常識が存在していたとしても、上記(1)のとおり、甲2文献の第8欄58ないし60行には、「検知された後(おそらく複数回)、信号電荷パケットはダイオードドレインを介して除去することができる。」という本件技術常識とは矛盾する記載があるのみならず、甲2発明は、ノイズが多いという課題に対して合算ウェルを設け、かつ、入力インピーダンスが高い(無限大である)電圧モード増幅器を用いるという手段によって、電荷の検出を複数回実行可能とし、それによってノイズを低減したものであって、複数の画素の電荷を合算することによってノイズ性能を向上させることはピクセルビニングと呼ばれる周知技

術を採用しており、この周知技術は本件技術常識と相反するものであることからすると、甲2発明は、本件技術常識を採用することなく、「電荷を複数回検出した後に、信号電荷パケットを除去する(リセットする)」という構成を採用している。

したがって、本件技術常識があるとしても、甲2発明は本件技術常識 を採用していないから、本件発明と甲2発明には相違点2が存在する。

## (3) 取消事由2 (相違点3の看過)

#### ア 相違点3

(ア) 本件発明に係るTDIラインイメージセンサは、M個のCCDが一列配列されたラインセンサーと(構成要件A)、M個の増幅器(構成要件C)と、M個のAD変換器(構成要件D)とを含むものであり、M個の増幅器のそれぞれは、ラインセンサーに配列されたM個のCCDのそれぞれに蓄積された電荷の並列入力を受け(構成要件C)、また、M個の変換器のそれぞれは、M個の増幅器から出力される各信号をAD変換する(構成要件D)。

このように、本件発明のラインセンサーは、M個のCCDを一列配置したものであり、かつ、M個の増幅器及びM個のAD変換器が設けられている。そして、M個のCCDのそれぞれに蓄積された電荷をM個の増幅器によって並列入力を受けて増幅し、M個の増幅器から出力される各信号をM個のAD変換器によってAD変換する構成となっている。

(イ) これに対し、甲2文献の図12をみると、ピクセルの各列に増幅器 1208が設けられている (構成2b、2c)が、本件発明のAD変換 器に相当し得る「アナログデジタル変換器1220」は、1つのユニットとして図示されており、詳細な内部構成は不明である。

そうすると、甲2発明における増幅器1208及びアナログデジタル 変換器1220が本件発明における増幅器及びAD変換器にそれぞれ

12

5

10

15

20

25

対応するものであるとしても、本件発明と甲2発明を対比すると、本件 決定が認定した相違点に加え、以下の相違点3も認定されるべきである。 「相違点3〕

本件発明のラインセンサーはM個のCCDが一列配置したものであり、かつ、M個の増幅器及びM個のAD変換器が設けられており、M個のCCDのそれぞれに蓄積された電荷をM個の増幅器によって並列入力を受けて増幅し、M個の増幅器から出力される各信号をM個のAD変換器によってAD変換するのに対し、

甲2発明のラインセンサーはM個のCCDを一列配置したものであり、かつ、M個の増幅器が設けられているが、アナログデジタル変換器は1つのユニットであり、M個のCCDのそれぞれに蓄積された電荷をM個の増幅器によって並列入力を受けて増幅するものの、M個の増幅器から出力される各信号を各AD変換器によってAD変換するのか不明である点。

(ウ) 本件発明は、出力部における信号処理速度が高くないという従来の TDIイメージセンサの問題(【0011】ないし【0014】)に対して、M個のカラム別にそれぞれ蓄積された電荷をM個のカラム別に並列 に増幅してAD変換するという相違点3の構成によって信号処理速度を 高速化したものであり、設計的事項といえるものではなく、相違点3は 容易想到性の判断の結論に影響するものである。

#### イ 被告の主張について

10

15

20

25

被告は、後記2(3) ウのとおり、各「増幅器1208」により出力された信号は、同時に「アナログデジタル変換器1220」に入力されるから、仮に、増幅器の個数と異なる個数のアナログデジタル変換器が複数の増幅器からの信号を同時に処理することにすると、各画素からの信号を混合して処理することになってしまう旨主張する。

しかし、アナログデジタル変換器の数を減らすべく、センサ(画素)からの読み出しを行うに際して、1つの増幅器につき1つのアナログデジタル変換器を設けるのではなく、複数の増幅器につき1つのアナログデジタル変換器を設けて(被告が主張する「増幅器の個数と異なる個数のアナログデジタル変換器を設けること」)、時分割でAD変換を行うことは、本件優先日当時において広く知られている手法である(甲24ないし27)。

そうすると、増幅器とアナログデジタル変換器の数が異なる技術事項も 従来から広く知られていたから、甲2発明において、1つのユニットであ るアナログデジタル変換器1220に複数のAD変換器があるとしても、 その数は不明であるというべきであって、相違点3は認定されるべきであ る。

# (4) 小括

10

15

20

25

以上によれば、本件決定には相違点の看過の誤りがあり、こうした相違点の看過は本件発明の容易想到性の判断の結論に影響するものであるから、本件決定は取り消されるべきである。

#### 2 被告の主張

(1) 甲2発明の認定の誤りの主張に対し

ア 一般に、引用発明の認定に当たっては、本件発明の発明特定事項に相当 する事項を過不足のない限度で認定すれば足り、特段の事情がない限り、 本件発明の発明特定事項との対応関係を離れて、引用発明を必要以上に限 定して認定する必要はない。本件決定で認定した甲2発明は、TDIイメ ージャとして本件発明の発明特定事項に相当する事項を過不足なく認定 している。

原告が言及する「電荷保存ノードが1つのラインセンサーの電荷の入力を受けること」及び「電荷保存ノードをリセットさせること」に関連する 事項は、本件発明では構成要件Hに「前記電荷保存ノードが1つのライン センサーの電荷の入力を受けることと、前記電荷保存ノードをリセットさせることと、が交互に行われる」と特定されており、それのみである。

そして、甲2発明の「ピクセルの各列は、センスノードに接続」されており、「センスノード」は、本件発明の構成要件Fの「前記画素部のN個の前記ラインセンサーのうち最後のラインセンサーから電荷が移動して蓄積された電荷保存ノード」ということができるから、甲2発明において、電荷が「ピクセルの各列」から「センスノード」まで移動し、「センスノード」が電荷を受け入れ、後段の増幅器へその値を出力できるようになった状態が本件発明の構成要件Hの「電荷保存ノードが1つのラインセンサーの電荷の入力を受けること」に相当する。また、甲2発明がTDIイメージャとして機能するためには、次の電荷の受入れに際して、先に受け入れた電荷をセンスノードからリセットすることは、後記イのとおり技術常識(本件技術常識)であり、これは、本件発明の構成要件Hの「電荷保存ノードをリセットさせることが、交互に行われる」ことに相当するものである。

したがって、本件決定は、甲2発明について、本件発明の構成要件Hに相当する事項を過不足なく認定しており、甲2発明の認定に誤りはない。イ なお、ラインセンサー等のCCD型固定撮像装置の技術分野において、電荷保存ノードに対して電荷を検出した後に電荷やノイズを完全に除去するためのリセットを行い、その後に次の電荷の入力を受け付けるという一連の動作を繰り返すことは、信号電荷を検出する方式としてFGA又はFDAであるか否かにかかわらず、本件優先日当時における技術常識(本件技術常識)である(乙2、3、5ないし7)。

## (2) 取消事由1 (相違点2の看過) について

10

15

20

25

ア 上記(1)のとおり、本件発明と甲2発明とは、「電荷保存ノードが1つの ラインセンサーの電荷の入力を受けることと、電荷保存ノードをリセット させることと、が交互に行われる」点で一致するものであり、原告が主張 する相違点2又は相違点2'はいずれも存しない。

原告は、相違点2に関し、「甲2発明では、電荷保存ノードが1つのラインセンサーの電荷の入力を複数回受けた後に、電荷保存ノードをリセットさせる場合が有り」と認定しているが、上記(1)のとおり、甲2発明は、電荷保存ノードが1つのラインセンサーの電荷の入力を受けることと、電荷保存ノードをリセットさせることが交互に行われるものであって、電荷保存ノードをリセットする前に、電荷保存ノードが1つのラインセンサーの電荷の入力を複数回受けるものではない。

イ 原告は、前記1(2)ウ(イ)のとおり、仮に本件技術常識があるとしても、 ①甲2文献の「検知された後(複数回)、信号電荷パケットは、ダイオード ドレイン(図9には示されていない)を介して除去され得る」という記載 や、②ノイズを低減させるために「合算ウェル」を用いるという記載は、 本件技術常識と矛盾するので、甲2発明は本件技術常識を採用するもので はない旨主張する。

10

15

20

25

しかし、甲2文献には、「検知された後(おそらく複数回)、信号パケットは、…除去され得る」との記載はあるものの、当該記載の「検知」は、「センスノード」が電荷を受け入れた後であって、リセットされる前(電荷の受け入れとリセットの間)に行われるもの、すなわち、①「センスノード」が電荷を受け入れ、②検知された後(おそらく複数回)、③「センスノード」から信号電荷パケットが除去されるという一連の構成が記載されており、本件技術常識は①と③に係るものであり、②の記載は本件技術常識と矛盾するものではない。

また、甲2文献の第6欄61行~7欄16行には、「他の実施形態では、 合算ウェル608を採用しなくてもよい。(中略)したがって、積分期間の 後、収集された電荷は、1つの画素604から直列に次の画素に転送され、 最後に、合算ウェルが採用されていない実施形態では、最後のウェル614に転送されてもよい。(中略)ここでも、ノイズ性能を向上させるために、センスノード804の直前に合算ウェル608を使用してもよい。」との記載があり、甲2発明において「合算ウェル」を採用することは必須でないことがわかる。本件決定は、甲2発明の認定において、「合算ウェル」を採用していない態様を基に認定したものであり、「合算ウェル」が本件技術常識と矛盾する構成であっても、甲2発明はそもそも「合算ウェル」を備えるものではないから、本件技術常識を踏まえて甲2発明を認定することに何らの誤りはない。

## (3) 取消事由2 (相違点3の看過) について

10

15

20

25

ア 甲2文献の第9欄33~36行には、「For purposes of clarify of illustration, not every column(row) of pixels is shown with associated sense node 804 or amplifiers 1208, or other components subsequently described in connection with the figure.」(訳:図面を明確にするために、画素のすべての列(行)が、関連付けられたセンスノード804又は増幅器1208、又は図に関連して説明される他のコンポーネントと一緒に示されているわけではない。)という記載があり、また、図12には、「増幅器1216」と上下方向に並んで、3つの「・・・」という記号の記載があり、「アナログデジタル変換器1220」と「シリアライザ1224」とが接続する箇所においては、2つの増幅器1216からの出力線に対応する位置に接続線の記載がある。ここで、増幅器1216はそれぞれの画素からの出力に対応して設けられているものであるから、「・・・」という記号は、当業者であれば、本来は多数の増幅器1216が存在するものが図面上省略されていることを意味するものと理解できる。

そして、技術的にみると、甲2発明のTDIイメージャにおいては、読み出し(検出)は列ごとに行われるから、各列の「センスノード804」

が受け入れた電荷の値は、各列に対応した「増幅器1208」が増幅し、 それに1対1に対応する「増幅器1216」を経由して、同時に「アナロ グデジタル変換器1220」に入力され処理されるものと理解できる。

そうすると、甲2発明において、M個の増幅器1208から出力される それぞれの信号をM個のアナログデジタル変換器によってアナログデジ タル変換することは、当業者にとって明らかであって、原告が主張する相 違点3は存しない。

イ 仮に、本件発明と甲2発明の対比において、甲2発明のAD変換器の数は不明であるという相違点3が存在するとしても、増幅器とAD変換器とは1:1で設けることが一般的である(甲24の【0076】、甲26の【0308】、甲27の【0188】)から、相違点3は、実質的な相違点ではないか、甲2発明において増幅器とアナログデジタル変換器の数を同じくすることは、当業者にとって容易に想到し得たものである。

10

15

20

25

ウ 原告は、前記1(3)イのとおり、アナログデジタル変換器(ADC)の数を減らすべく、センサ(画素)からの読み出しを行うに際して、複数の増幅器につき1つのADCを設けて時分割でAD変換を行うことは広く知られている手法であり、増幅器とアナログデジタル変換器の数が異なる技術事項も従来から知られていたから、甲2発明において1つのユニットであるアナログデジタル変換器1220内に複数のAD変換器があるとしても、その数は不明であり、相違点3が認定されるべきである旨主張する。

しかし、各「増幅器1208」により出力された信号は、同時に「アナログデジタル変換器1220」に入力されるから、仮に、増幅器の個数と異なる個数のアナログデジタル変換器が複数の増幅器からの信号を同時に処理することにすると、各画素からの信号を混合して処理することになってしまうが、甲2発明にはそのようなことを可能にする構成が記載されてはいない。

甲2発明は、「アナログデジタル変換器1220」の出力がパラレル信号として「シリアライザ1224」に入力され、「シリアライザ1224」によりシリアル信号に変換される構成であるから、仮に、複数の増幅器の出力に対して時分割でAD変換を行うという構成を採用する場合には、増幅器とアナログデジタル変換器1220との間に時分割処理をするための構成が必要となるが、甲2文献の図12には、「アナログデジタル変換器1220」と「シリアライザ1224」とが接し、2本の接続線を含む構成が記載されるのみで、時分割でAD分割変換処理された信号をシリアライザに入力するための構成の存在を認めることができない。また、甲2発明において時分割で変換を行う構成を備えるということは、パラレル信号をシリアル信号に変換してAD変換を行い、その後にシリアル信号をパラレル信号に変換した後に「シリアライザ1224」により再びパラレル信号をシリアル信号に変換するといった2段階のシリアル化を行う構成を意味するが、甲2発明がそのような複雑な構成を採用する意味を見いだせない。

#### (4) 小括

10

15

20

25

以上によれば、原告が主張する取消事由はいずれも理由がない。

#### 第4 当裁判所の判断

1 本件明細書の記載事項

本件明細書(ただし、本件訂正後のもの。)には別紙1のとおりの記載があり、 別紙1の記載を総合すれば、本件明細書には以下のとおりの開示があることが 認められる。

(1) TDIラインイメージセンサーは、ラインセンサーがスキャン方向に複数段配列されたものであり、各ラインのCCDで蓄積された電荷を隣接した次のラインのCCDに並行移動により最後のラインまで移動させて蓄積した後、最後のラインに蓄積された電荷を垂直移動させて信号処理部に出力する

ことによって、ライン単位で各セルに対して順次データを処理することができるようにするものであるが、CCDに蓄積された電荷を信号処理部に出力するために垂直移動する時は停止した状態で一つずつ直列移動させて転送するため、垂直移動時に多くの時間を要するという問題があり、特に、TDIラインイメージセンサーは、各ラインに沿って一列配列されたCCDの数が相対的に多いため、TDIラインイメージセンサーを通じてイメージをスキャンするために要する多くの時間が、蓄積された電荷を垂直移動させて出力することに起因するという問題点があった(【0010】、【0012】ないし【0014】。

「本発明」の目的は、こうした問題点を解決するために、CCD素子を通じてTDI(Time Delay Integration)方式で電荷を蓄積するように画素部を構成し、出力部はCCDで蓄積された各コラムの電荷をAD変換してメモリーバッファーに保存した後順次出力するように構成することによって、CD素子としてCMOS素子の特性による解像度と転送速度を向上させるだけでなく、消費電力とノイズを低減させることができるようにしたTDIラインイメージセンサーを提供することにある( $\{OO15\}$ )。

(2) 「本発明」のTDIイメージラインセンサーは、M個のCCDが一列配列されたラインセンサーと、スキャン方向に並列にN個のラインセンサーが配列されてラインセンサーのコラム別に蓄積された電荷を並列方向に移動させて蓄積する画素部と、画素部に蓄積された電荷をコラム別に並列入力を受けてAD変換して保存した後順次出力する出力部を含むことを特徴とし、「本発明」における出力部は、画素部に蓄積された電荷をコラム別に電荷保存ノードに並列入力を受けてそれぞれ増幅するためのM個の増幅器と、増幅器から出力される各信号をAD変換するM個のAD変換器と、AD変換器の出力を保存して順次出力するメモリーバッファーを含むことを特徴とし、「本発明」における増幅器は、ソースフォロワ増幅器であることを特徴とする(【0

016】ないし【0018】)。

2 引用文献(甲2文献)の記載事項

10

15

20

25

本件優先日前に頒布された刊行物である甲2文献には、別紙2のとおりの記載(ただし、訳文)があり、この記載によれば、次のような開示があるものと認められる。

(1)ア 電荷結合素子(CCD)は、優れた光学性能を持つことが証明されているため、高性能な光子検出器にはCCDセンサがよく取り上げられ、また、航空宇宙センサの分野では、TDI CCDが軌道上での観測に非常に適しているとされているが、CCDは比較的消費電力が大きく、消費電力が気になる機器ではCMOSデバイスが好ましいが、CMOS光子センサはCCDに比べてノイズが多く光学性能が劣り、また、COMS光子センサのみではTDI機能を実現することが難しい(第1欄19行~47行)。

このため、CCD光子検出器の優れた光学性能とCMOSプロセスにより可能となる低消費電力及び高密度実装を組み合わせた光子センサの作成が望まれるが、1枚の基板上でCCD及びCOMSプロセスを組み合わせることは困難であり、また、CCD及びCMOSの両方の技術を用いて単一の基板上に製造されたデバイスは、電荷移動効率の悪さ及びプロセスが最適化されていないことによるノイズの多さのため不十分な画像品質が問題となり、こうした両立しがたい製造プロセス技術を統合することを避けるため、第2のプロセスを用いた第2の基板(CMOS読み出し等)を相互接続した第1のプロセスを用いた第1の基板(CCD光子検出器等)に形成された構造を利用するデバイスが開発されてきているが、電荷の検出は一般的に特定の電荷の収集に対して1回だけ実行できることに留意すべきであり、また、CCDから増幅されていない信号やバッファされていない信号を供給すると、多くの場合、劣化した信号をもらすことになる(第1欄48行~第2欄7行)。

- イ 本発明は、これらの問題及び先行技術の欠点等を解決することにあり、本発明の1つの実施形態は、列(パラレル)出力において、又は近くで、CCDからデータを抽出し、その結果、電力を大量に消費するシリアルシフトレジスタを取り除くことにより、CCDの電力損失を劇的に削減することができるという事実に基づくものであり、本発明は、CCD光子検出器とCMOS回路読み出し回路を組み合わせることで、現状の技術に比べて大きな利点が得られる(第2欄13行~24行)。

- (2) そして、甲2文献には、①「CCDイメージセンサアレイ124は、複数のサブアレイ1204にまとめられた複数のピクセル604を含む。ピクセル604の各列(行)は、センスノード804aと関連していてもよい。」(9欄24~27行、図12)、②「センスノード804は、典型的には、フローティングディフュージョンへのコンタクトを有する。」(第6欄60行から61行)、③「図示されているように、第1の半導体基盤126上に形成される増幅器1208は、各センスノード804に関連していてもよい。」(第9欄30~33行、図12)、「電圧バッファされた出力を提供するために、増幅器1208は、ソースフォロア…を構成してもよい。」(第9欄39行~41行)との記載があり、これらの記載によれば、「CCDイメージセンサアレイ124は、複数のサブアレイ1204に属するピクセルを含み」(2a)、「ピクセルの各列は、センスノード804に接続し、センスノード804は、フローティングディフュージョンへのコンタクトを有し、」(2b)、「各センスノードは、増幅器1208が接続され、増幅器は、ソースフォロアで構成され、」(2c)との発明特定事項を含む発明が記載されているといえる。

また、「…センスノード804から電圧モード増幅器820への電圧信号を運ぶための信号ライン906は、リセットスイッチ又はトランジスタ908に接続される。…検知された後(おそらく複数回)信号電荷パケットはダイオードトレイン(図9には示されていない)を介して除去され得る。」(第

8欄46行~60行)、「図12に示すように…リセットスイッチ908は、接続されたセンスノード804をリセットするために、第1の半導体基板に形成することができる。」(10欄13行~20行)との各記載並びに図9及び図12からすると、甲2文献には、「各センスノード804には、当該センスノード804をリセットするためのリセットトランジスタが接続され、当該リセットトランジスタは、ゲートとVresetに接続されたダイオードドレインを有し、」(2d)、「各センスノード804に蓄積された電荷が複数回検知された後、各センスノード804の信号電荷パケットが除去される場合があり、」(2d')との発明特定事項を含む発明の記載があることが認められる。

10

15

20

25

次いで、甲2文献には、「一つのピクセルからの信号又はTDI配置の多数のピクセルから統合された信号は、アナログデジタル変換器(ADC)1220により処理される。 $\cdots$ ADCによりデータがデジタル化された後、第2の半導体基板130上に形成されたシリアライザ1224によってデジタル処理される。」(第10欄30行~39行)との記載があるから、「ピクセル信号は、アナログデジタル変換器1220により処理され、シリアライザ1224に処理される」(2e)との発明特定事項を有する発明の記載があり、また、「他の実施形態では、電荷は、連続する積分期間中に連続する画素604に蓄積されてもよい。この蓄積された電荷の実質的にすべてが、その後、最後のウェル614に転送される。このプロセスは、当業者にはTDI(時間遅延積分)としても知られている。」(第7欄10行~15行)との記載があるから、甲2文献には「TDIイメージャ」に関する発明の記載もあることが認められる。

(3) 以上によれば、甲2文献には、「CCDイメージセンサアレイ124は、 複数のサブアレイ1204に属するピクセルを含み、ピクセルの各列は、センスノード804に接続し、センスノード804は、フローティングディフ ュージョンへのコンタクトを有し、各センスノードは、増幅器1208が接続され、増幅器は、ソースフォロアで構成され、各センスノード804には、当該センスノード804をリセットするためのリセットトランジスタが接続され、当該リセットトランジスタは、ゲートとVresetに接続されたダイオードドレインを有し、各センスノード804に蓄積された電荷が複数回検知された後、各センスノード804の信号電荷パケットが除去される場合があり(下線部は当審で引いたもの。以下、この下線部を「2d'の構成」という。)、ピクセル信号からの信号は、アナログデジタル変換器により処理され、シリアライザ1224に処理されるTDIイメージャ」の発明が記載されているものと認められる。

#### 3 技術常識について

10

15

20

25

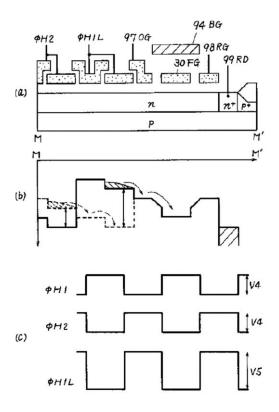

- (1)ア(ア) 本件優先日前に頒布された刊行物である乙5文献には、別紙3の 1のとおりの記載があり、同記載を総合すると、同文献には、FGAタ イプを採用した、固体撮像装置に用いられる電荷転送デバイスより成る 埋込チャンネルCCD(BCCD)のCCD遅延線において、時点t1 ~t4までの間に1回、信号電荷 q 1を読み取り処理し、t5で信号電 荷を廃棄し、t6で新たな信号電荷 q 2を転送し、信号電荷 q 2も q 1 と同様の処理が繰り返されることが開示されている。

- (イ) 本件優先日前に頒布された刊行物である乙6文献には、別紙3の2のとおりの記載があり、同記載を総合すると、同文献には、CCDの電荷検出装置等に関するものにおいて、フローティングゲートに転送されてきた信号電荷Qは、次の信号電荷が転送される前にRD99に吸収され、前の信号電荷がリセットされた後に次の信号電荷の入力が受け付けられることが開示されているものと認められる。

- (ウ) 本件優先日前に頒布された刊行物である乙7文献には、別紙3-3 のとおりの記載があり、同記載を総合すると、同文献には、電荷検出方

式としてFGAタイプを採用した固体撮像装置において、信号電荷を読み出した後に、リセットゲート26をHighにして、チャネル領域21からリセットドレイン27に電荷の吐き出しを行うことが開示されているものと認められる。

イ 前記ア(ア)ないし(ウ)の各文献の記載を総合すると、撮像素子としてCCDを用いた固体撮像装置において、信号電荷の検出方式としてFGAタイプを採用したとき、信号電荷の入力を受けた後、次の信号電荷が転送される前に信号電荷がリセットされることは、本件優先日当時における技術常識であったと認められる。

10

15

20

25

ウ これに対し、原告は、前記第3の1(2)ウ(ア)のとおり、甲2発明は、F G A タイプであるのに対し、乙7文献に記載された発明は、F G A タイプであるとはいえないから、これらは甲2発明に採用されている技術常識を認定する根拠になり得ず、仮にF G A タイプであるとしても、甲2発明における「浮遊ゲート904のリセット」に対応する事項の開示はなく、また、乙6文献は、甲2発明における浮遊ゲート904のリセットの開示がないから、甲2発明に採用されている技術常識を認定する根拠となり得ない旨主張する。

しかし、乙7文献には、「信号電荷検出部が基本的にはFG方式の一種であるものの、FG方式以上の高変換利得を得ることができる。」(【0011】)、「上記固体撮像装置1は、基本的にはFG方式の固体撮像装置の一種であるものの、FG方式以上の高変換利得を得ることが可能である。」(【0020】)との記載があるように、同文献で採用されている固体撮像装置における信号電荷検出部にはFGAタイプが採用されていることを前提とするものである。

また、技術常識は、技術的に共通する複数の各文献で採用されている様々な構成を前提としつつ、抽出することができる共通の技術事項を認定する

ものであるところ、原告の上記主張は、甲2発明で採用されている構成が 乙6文献や乙7文献に開示されていないことを問題とするものにとどま るから、採用の限りではない。

- (2)ア 本件優先日前に頒布された以下の刊行物には、以下のとおりの記載がある。

- (ア) 特開2007-281540号公報(甲24。公開日平成19年10月25日)

#### [0001]

10

15

20

25

本発明は、物理量分布検出装置および撮像装置に関し、特に列並列型AD(アナログーデジタル)変換装置を搭載した物理量分布検出装置および当該物理量分布検出装置である固体撮像装置を撮像デバイスとして用いた撮像装置に関する。

#### [0076]

なお、上記各実施形態では、比較器 31 を含む ADC23(23-1~23-m)が、列信号線 14-1~14-mに対して、画素ピッチに合わせて画素列の数だけ、即ち 1 対 1 の対応関係をもって配置されてなる AD 変換装置に適用した場合を例に挙げて説明したが、本発明はこの適用例に限られるものではなく、複数本の列信号線 14 に対して 1 つの ADC23 を配置し、当該 ADC23 を時分割で使用する構成の AD 変換装置に対しても同様に適用可能である。」

(イ) 特開2014-23065号公報(甲26。公開日平成26年2月3日)

## [0001]

本技術は、固体撮像装置、及び製造方法に関し、特に、例えば、行方向に並ぶ複数のAD変換器を有する、いわゆる列並列型のAD変換部を備えるイメージセンサ等の固体撮像装置において、隣接する列どうしの

AD変換器を構成するコンパレータの間のクロストーク特性を、副作用なしで改善することができるようにする固体撮像装置、及び、製造方法に関する。

# [0308]

また、本実施の形態では、列並列AD変換部22において、画素アレイ10の画素 $11_{m,n}$ の一列に対して、1つの $ADC31_n$ を設けることとしたが、列並列のAD変換部22では、その他、例えば、画素アレイ $11_{m,n}$ の2列等の複数列に対して、1つのADCを設け、1つのADC において、画素 $11_{m,n}$ の2列等からの電気信号を、時分割でAD変換することができる。」

(ウ) 特開2013-51527号公報(甲27。公開日平成25年3月 14日)

#### $[[0\ 0\ 0\ 1\ ]]$

10

15

20

本発明は、固体撮像装置及び撮像装置に関する。

## [0188]

なお、上記第1~第5の実施形態では、比較器を含むAD変換器が画素ピッチに合わせて画素列の数だけ、即ち画素列に対して1対1の対応関係で配置されている場合を例に説明したが、本発明はこの適用例に限られるものではない。つまり、複数本の垂直信号線22に対して1つのAD変換器を配置してもよい。この場合、このAD変換器は、時分割で対応する複数本の垂直信号線22に出力された信号電圧をAD変換する。

- イ 上記の各文献の記載を総合すると、固体撮像装置におけるAD変換器には、画素列に対して1:1の対応関係で配置されるものがあることは、本件 優先日当時における技術常識であったと認められる。

- 25 4 相違点2の看過(取消事由1)について

- (1) 原告は、前記第3の1(2)のとおり、本件発明と甲2発明には、本件決定

が認定した相違点のほか、甲2発明には「各センスノード804に蓄積された電荷が複数回検知された後に、各センスノード804の信号電荷パケットが除去される場合もあり」(2 d')との構成を備えていることを前提として、本件決定には相違点2の看過がある旨主張するところ、前記2(3)のとおり、甲2発明は、原告が主張する2 d'の構成を備えているため、以下、これを前提にして検討する。

(2) 甲2発明の2 d'の構成は、「検知された後(おそらく複数回)、信号電荷パケットは、ダイオードトレイン(図9には示されていない)を介して除去され得る。」(第8欄58~60行)に対応するものであるところ、検知される信号電荷パケットは、1つのパケットであるのか複数のものであるのかについて同記載からは必ずしも明らかではない。

もっとも、甲2文献の他の実施例に関する記載を見てみると、図7の実施例に関して、「…相互接続404a-bによってセンスノード804からの電圧信号が供給されるので、1つの電荷の収集の複数の測定値を提供するために、センスノード804の電圧を複数回読み取ることができる。したがって、信号対雑音比を改善するために、センスノード804内の、又はセンスノード804に関連する電荷の複数のサンプル(測定値)を取ることができる。」(第7欄55~63行)と、一つの信号電荷のパケットがセンスノード804に伝達されるごとにセンスノードの電圧を複数回読み取ることができることが記載されており、また、図8の実施例に関して、「画素604の1つからの画像信号に関連付けられた電荷がポテンシャルウェル818に転送されると、ゲート806上の電圧変化が検知され得るように導入される。…検知された後、信号電荷パケットは、ポテンシャルウェル818から転送され、ダイオード830及びダイオードドレイン832を介して除去されてもよいし、あるいは、ノイズ低減のために複数のサンプルを可能にするためにフローティングゲート806の下に残ってもよい。所望の数のサンプルが得られ

た後、電荷は、ダイオードトレイン832を介して除去され得る。」(第8欄23~35行)と、1つの信号電荷を検知した後、ダイオードトレイン832を介して除去してもよいし、ノイズ低減のために複数を残してもよく、所望の数のサンプルが得られた後、電荷をダイオードトレインを介して除去することが記載されている。

このように、甲2文献においては、複数回検知する場合があるときは、単一の信号電荷パケットを前提にしており、複数の信号電荷パケットについて複数回検知する構成については特段の記載も示唆も見当たらないし、同文献(第6欄50行~第7欄43行)には、図6に関する実施例として、「ノイズ性能を向上させるために、センスノード804の直前に合算ウェル608を使用してもよい。」との記載があるが、ここでも複数の信号電荷パケットを「合算」する旨の記載は見当たらない。

10

15

20

25

そうすると、甲2文献の「検知された後(おそらく複数回)、信号電荷パケットは、ダイオードトレイン(図9には示されていない)を介して除去され得る。」(第8欄58~60行)との記載は、単一の信号電荷パケットを複数回検知した後、信号電荷パケットはダイオードトレインを介して除去され得ることを記載したものであるといえるから、「各センスノード804に蓄積された電荷が複数回検知された後、各センスノード804の信号電荷パケットが除去される場合があり」(2d'の構成)は、各センスノード804に蓄積された単一の信号電荷パケットの電荷が複数回検知された後、各センスノード804の信号電荷が除去される場合があるとの構成であることになる。

こうした構成を前提とした上で、甲2発明と同じく、FGAタイプを用いた信号電荷の検出方式において、信号電荷の入力を受けた後、次の信号電荷が転送される前に信号電荷がリセットされることは、本件優先日当時の技術常識であったことを踏まえると、甲2発明においても、本件発明における「前記電荷保存ノードが1つのラインセンサーの電荷の入力を受けることと、前

記電荷保存ノードをリセットさせることと、が交互に行われる」(構成要件H) の構成を備えているといえる。

したがって、甲2発明における2d'の構成は、本件発明との相違点となるものではない。

(3) これに対し、原告は、前記第3の1(2)ア(イ)のとおり、ライセンサーからの電荷入力を複数回受けた後にリセットを行うという動作は、複数ラインからの電荷入力を積算することを意味することを前提として、同ウ(イ)のとおり、甲2発明において、複数の画素の電荷を合算することによってノイズ性能を向上させるということは、ピクセルビニングと呼ばれる周知技術を採用したものであり、こうした周知技術は本件技術常識と相反するものであるから、甲2発明には本件技術常識は採用されていない旨主張する。

しかし、前記(2)のとおり、甲2文献の「検知された後(おそらく複数回)、信号電荷パケットは、ダイオードトレイン(図9には示されていない)を介して除去され得る。」との記載は、単一の信号電荷パケットを複数回検知した後、信号電荷パケットはダイオードトレインを介して除去され得ることを記載したものであるといえるから、原告の上記主張はその前提を欠くものであって、理由がない。

- (4) 以上によれば、本件決定には、甲2発明について2d'の構成を認定をしていない点で誤りがあるものの、原告が主張する相違点2(又は相違点2')は存しないから、本件決定は結論において相当であり、原告主張の取消事由1は理由がない。

- 5 取消事由2 (相違点3の看過)

10

15

20

25

(1) 原告は、前記第3の1(3)のとおり、本件決定は、本件発明と甲2発明の対比において相違点3、すなわち、本件発明のラインセンサーはM個のCCDが一列配置したものであり、かつ、M個の増幅器及びM個のAD変換器が設けられており、M個のCCDのそれぞれに蓄積された電荷をM個の増幅器

によって並列入力を受けて増幅し、M個の増幅器から出力される各信号をM個のAD変換器によってAD変換するのに対し、甲2発明のラインセンサーはM個のCCDを一列配置したものであり、かつM個の増幅器が設けられているが、アナログデジタル変換器は1つのユニットであり、M個のCCDのそれぞれに蓄積された電荷をM個の増幅器によって並列入力を受けて増幅するものの、M個の増幅器から出力される各信号をAD変換器によってAD変換するのか不明である点について、相違点の看過がある旨主張するので、以下検討する。

(2)ア 本件発明は、「M個のCCDが一列配列されたラインセンサー」(構成要件A)、「前記画素部に蓄積された前記電荷をコラム別に電荷保存ノードに並列入力を受けてそれぞれ増幅するためのM個の増幅器:」(構成要件C)、「前記増幅器から出力される各信号をAD変換するM個のAD変換器;および」(構成要件D)との発明特定事項を有するものであるから、本件発明の「ラインセンサーはM個のCCDが一列配置したものであり、かつ、M個の増幅器及びM個のAD変換器が設けられており、M個のCCDのそれぞれに蓄積された電荷をM個の増幅器によって並列入力を受けて増幅し、M個の増幅器から出力される各信号をM個のAD変換器によってAD変換する」ものであるといえる。

これに対し、甲2発明は、「CCDイメージングセンサアレイ124は、複数のサブアレイ1204に属するピクセル604を含み、」(2a)、「ピクセルの各列はセンスノード804に接続し、」(2b)、「各センスノード804には、増幅器1208が接続され」(2c)、「TDIイメージャ」(2f)との構成を有するものであり、複数のサブアレイ1204の数、センスノードの数及び増幅器1208の数はいずれも等しい構成であると理解できるが、「ピクセルからの信号は、アナログデジタル変換器1220により処理され、シリアライザ1224により処理される」(2e)との構成

からは、アナログデジタル変換器の個数については特定されていない。ここで、甲2文献の記載事項についてみると、図12には、アナログデジタル変換器1220については記載が省略されており、サブアレイ1204、センスノード及び増幅器の数と同一のものであるかは不明であり、増幅器1208がどのようにしてアナログデジタル変換器1220に入力されるかについての記載もない。

そうすると、甲2発明において、増幅器1208から入力されるアナログデジタル変換器の個数は不明であるというほかなく、増幅器とAD変換器が同数である本件発明とこの点において相違する(原告が主張する相違点3)。

10

15

20

25

イ これに対し、被告は、前記第3の2(3)アのとおり、甲2文献の図12の「増幅器1216」と上下方向に並んだ3つの「…」の記号は、当業者であれば、本来は多数の増幅器1216が存在するものが図面上省略されていることを意味するものと理解でき、甲2発明のTDIイメージャにおいては、読み出し(検出)は列ごとに行われるものであるから、各列の「センスノード804」が受け入れた電荷の値は、各列に対応した「増幅器1208」が増幅し、それに1対1に対応する増幅器1216を経由して同時にアナログデジタル変換器1220に入力され処理されると理解できるから、相違点3は存在しない旨主張する。

しかし、前記 3(2) アの各文献の記載に加え、特開平 6-197285号 公報 (甲 25。公開日平成 6 年 7 月 15 日) には、「第 2 の発明においては、撮像素子から得られる 2 つの色信号を時分割的に切換えるスイッチ手段を設けている。」(【 0018】)、「第 2 の発明によれば、スイッチ手段から時分割で得られる 2 つの色信号を共通の A D変換器に加えることにより、記録時に用いられる A D変換器が削減できる」(【 0020】)との記載があることを総合すると、固体撮像装置における A D変換器は、増幅器より少

ない数を設けることも、本件優先日当時における技術常識であったといえることからすると、甲2発明においても、各列の「センスノード804」が受け入れた電荷の値は、各列に対応した「増幅器1208」が増幅し、それに1対1に対応する増幅器1216を経由して同時にアナログデジタル変換器1220に入力され処理されるとは限らず、省略された図12の「…」の記載から、アナログデジタル変換器と増幅器が同数であると当業者であれば当然に理解するとまではいえないから、被告の上記主張は理由がない。

(3) 上記(2)のとおり、本件発明と甲2発明には、本件決定が認定した相違点のほかに相違点3があり、本件決定には相違点3の看過があるといえる。

もっとも、前記3(2)のとおり、固体撮像装置におけるAD変換器には、画素列に対して1:1の対応関係で配置されるものがあることは本件優先日当時における技術常識であるところ、甲2発明においては、複数のサブアレイ1204の数、センスノードの数及び増幅器1208の数はいずれも等しい構成であり、M個の増幅器から出力される各信号を変換するAD変換器の個数が不明であるとしても、上記技術常識を踏まえると、甲2発明においても増幅器の数とAD変換器の数も同一の構成を有するものであることは当業者であれば容易に想到するといえる。

そうすると、上記相違点3の看過は、容易想到性の結論に影響を及ぼすとはいえない。

(4) 以上によれば、本件決定には、相違点3の看過があるものの、本件決定の結論に影響を及ぼすものではないから、原告主張の取消事由2は理由がない。

#### 6 結論

10

15

20

25

以上によれば、原告が主張する取消事由はいずれも理由がなく、本件決定を 取り消すべき違法は認められない。よって、原告の請求を棄却することとして、 主文のとおり判決する。

# 知的財産高等裁判所第4部

|    | 裁判長裁判官 |   |   |   |   |  |

|----|--------|---|---|---|---|--|

| 5  |        | 菅 | 野 | 雅 | 之 |  |

|    |        |   |   |   |   |  |

|    | 裁判官    |   |   |   |   |  |

|    |        | 中 | 村 |   | 恭 |  |

| 10 |        |   |   |   |   |  |

|    | 裁判官    |   |   |   |   |  |

|    |        | 尚 | Щ | 忠 | 広 |  |

## (別紙1)

#### 【発明の詳細な説明】

#### 【技術分野】

#### [0001]

本発明はTDIラインイメージセンサーに関するもので、より詳細にはCCD素子を通じてTDI(Time Delay Integration)方式で電荷を蓄積するように画素部を構成し、出力部はCCDで蓄積された各コラムの電荷をAD変換してメモリーバッファーに保存した後、順次出力するように構成することによってCCD素子とCMOS素子の特性による解像度と転送速度を向上させるだけでなく、消費電力とノイズを低減させることができるようにしたTDIラインイメージセンサーに関するものである。

# 【背景技術】

#### [0002]

最近、生産設備が大量化、自動化および精密化されるにつれて、人の肉眼または各種センサーに依存していた機能が次第にイメージセンサーを採用するビジョンマシン(vision machine)に代替されている傾向にある。このようなイメージセンサーに主に使用されている半導体素子が電荷結合素子(charge coupled devices; CCD)である。

## [0003]

20

CCDは一つの素子から隣接した他の素子に電荷を転送できる素子を意味する。 このようなCCDを採用したセンサーは光量による各セル(cell)内の自由電 荷量の変化を電気的信号に変換する構造を有する。

#### [0004]

構造的に、CCDは大きく、実際の光量によって電荷が蓄積されるセル領域およ び蓄積された電荷を順に転送する通路の役割をするシフトレジスター (shif tregister)で構成される出力部を含む。

# [0005]

CCDは各セルがどのようなアレイ(array)に配置されて映像を生成するかによって、領域スキャン(area scan)方式、ラインスキャン(line scan)方式、TDI(Time Delay Integration)ラインスキャン方式などに分かれる。

## [0006]

ラインスキャン方式のイメージセンサ(以下「ラインセンサ」という)は、画像 光を受光するピクセルがライン上に配列された1次元センサーである。2次元に広 げられた画像を撮像する場合には、ラインセンサまたは被写体を移動させて被写体 を一ラインずつ順に撮像する。

## [0007]

すなわち、ラインスキャン方式は一度に一ラインずつ任意の速度で露出および転送する方式であり、領域スキャン方式に比べて低費用で高速および高分解能映像を得ることができるという長所を有する。例えば、2048\*2048のフレームを得るために、領域スキャン方式は4Mのピクセル(pixell)数を必要とするのに反して、ラインスキャン方式は2Kのピクセルさえあれば2048\*2048だけでなく2048\*1000などの多様な大きさのフレームを得ることができる。

#### [0008]

しかし、高速で移動する被写体を撮影する場合や、ラインセンサーを高速に移動させて被写体を撮影するときのように、高速スキャンを遂行する場合、各ラインごとに高速で電荷の蓄積と転送を繰り返すことになるため、一ライン当たりに電荷を蓄積できる時間が短くなって画像の光量が不足する。このように、光量に対する要求が増加しても、照明装置の限界のために光量を無制限に増加させることができない。

#### [0009]

したがって、PPD (pinned-photodiode)、CMOSセンサな

どの材料を改善して感度を高める研究が進められている一方、複数のラインセンサーを並べて光量を累積させて感度を高める方法も提案されている。

#### [0010]

TDIラインスキャン方式のイメージセンサ(以下、「TDIラインイメージセンサ」という)は、ラインセンサーがスキャン方向に複数段配列されたもので、各ラインのCCDで蓄積された電荷を画像の移動と同期させて次のラインのCCDに転送する。このような過程を最後のラインセンサーまで繰り返して電荷を重ねた後出力することによって、結果的に高速スキャンにおいても光量を十分に満足する画像を得ることができる。

## $[0 \ 0 \ 1 \ 1]$

本発明の背景技術は、大韓民国公開特許公報第2009-0023573号(2009.03.05.公開、発明の名称: TDI-CCDイメージセンサーを制御するための方法) に開示されている。

#### 【発明の概要】

15 【発明が解決しようとする課題】

#### [0012]

このようなTDIラインイメージセンサーの場合、各ラインのCCDで蓄積された電荷を隣接した次のラインのCCDに並行移動により最後のラインまで移動させて蓄積した後、最後のラインに蓄積された電荷を垂直移動させて信号処理部に出力することによって、ライン単位で各セルに対して順次データを処理することができるようにする。

#### [0013]

前記において、CCDに蓄積された電荷を隣接したラインに並行移動させる時は 画像の移動と同期して並列に移動されるが、蓄積された電荷を信号処理部に出力す るために垂直移動させる時は停止した状態で一つずつ直列移動させて転送するため、 垂直移動時に多くの時間が要されるという問題点がある。

## [0014]

特に、TDIラインイメージセンサーの場合、スキャン方向に並列に配列された ラインの数よりは高い解像度のために、各ラインに沿って一列配列されたCCDの 数が相対的に多いため、TDIラインイメージセンサーを通じてイメージをスキャンするために要される多くの時間が蓄積された電荷を垂直移動させて出力すること に起因する問題点がある。

## [0015]

本発明は前記のような問題点を改善するために創出されたもので、本発明の目的はCCD素子を通じてTDI(Time Delay Integration)方式で電荷を蓄積するように画素部を構成し、出力部はCCDで蓄積された各コラムの電荷をAD変換してメモリーバッファーに保存した後順次出力するように構成することによって、CCD素子とCMOS素子の特性による解像度と転送速度を向上させるだけでなく、消費電力とノイズを低減させることができるようにしたTDIラインイメージセンサーを提供することである。

#### は 【課題を解決するための手段】

#### [0016]

本発明の一側面に係るTDIラインイメージセンサーは、M個のCCDが一列配列されたラインセンサーと、スキャン方向に並列にN個のラインセンサーが配列されてラインセンサーのコラム別に蓄積された電荷を並行方向に移動させて蓄積する画素部;および画素部に蓄積された電荷をコラム別に並列入力を受けてAD変換して保存した後順次出力する出力部を含むことを特徴とする。

#### [0017]

20

本発明において出力部は、画素部に蓄積された電荷をコラム別に電荷保存ノードに並列入力を受けてそれぞれ増幅するためのM個の増幅器;増幅器から出力される各信号をAD変換するM個のAD変換器;およびAD変換器の出力を保存して順次出力するメモリーバッファー;を含むことを特徴とする。

## [0018]

本発明において増幅器は、ソースフォロワ増幅器であることを特徴とする。

## 【発明の効果】

#### [0019]

本発明に係るTDIラインイメージセンサーは、CCD素子を通じてTDI(Time Delay Integration)方式で電荷を蓄積するように画素部を構成し、出力部はCCDで蓄積された各コラムの電荷をAD変換してメモリーバッファーに保存した後順次出力するように構成することによって、CCD素子とCMOS素子の特性による解像度と転送速度を向上させるだけでなく消費電力とノイズを低減させることができる。

#### 【発明を実施するための形態】

## [0023]

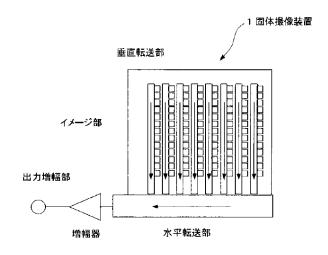

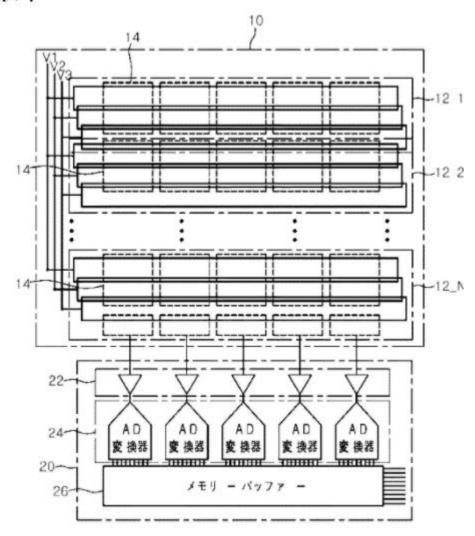

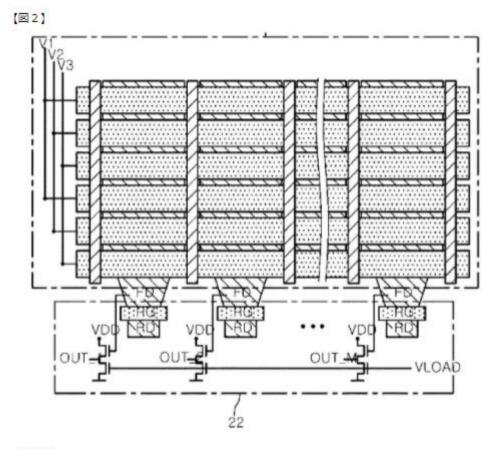

図1は本発明の一実施例に係るTDIラインイメージセンサーを示したブロック構成図で、図2は本発明の一実施例に係るTDIラインイメージセンサーの画素部の構造を示した図であり、図3は本発明の一実施例に係るTDIラインイメージセンサーで電荷の移動を説明するための図である。

#### [0024]

図1と図2に図示された通り、本発明の一実施例に係るTDIラインイメージセンサーは画素部10および出力部20を含む。

#### [00025]

#### [0026]

すなわち、図3に図示された通り、各CCD14のV1、V2、V3電圧を順に 制御することによって、CCD14に蓄積された電荷が隣接したCCD14に移動 され、これによって電荷保存ノード(FD)に重ねて出力される。

## [0027]

画素部10の構成は一般的なTDIラインイメージセンサーの画素部の構成と対応すれるため、本実施例ではその具体的な構成に対する説明は省略する。

#### 5 [0028]

出力部20は画素部10に蓄積された電荷をコラム別に並列入力を受けてAD変換して保存した後順次出力するように、増幅器22、AD変換器24およびメモリーバッファー26を含む。

#### [0029]

10 増幅器22は画素部10で蓄積された電荷をコラム別に電荷保存ノード(FD) に並列入力を受けてそれぞれ増幅するために、一つのラインセンサ12に配列されたCCD14の個数に対応するようにM個を具備する。

#### [0030]

この時、増幅器22は画素部10の最後のラインセンサ12\_Nから電荷が移動して蓄積された電荷保存ノード(FD)の電位によりターンオンされて電圧値を出力するソースフォロワ増幅器で構成することができる。

#### [0031]

AD変換器24はM個の増幅器22から出力される各信号をAD変換する。

## [0032]

20

メモリーバッファー26はM個のAD変換器24でデジタル信号に変換された画像信号を保存した後順次出力して信号処理部(図示されず)でライン別に画像信号を処理することができるようにする。

#### [0033]

このように構成されたTDIラインイメージセンサーをスキャンして撮影すると、 TDI方式で画素部10の各ラインセンサ12のCCD14に蓄積された電荷はス キャンと同期して隣接したラインセンサ12にコラム別に移動されて出力部20の

電荷保存ノード(FD)に出力される。

#### [0034]

電荷保存ノード(FD)に蓄積された電荷は増幅器 22を通じて増幅された後、AD変換されて信号(Signal)として出力される。以後、リセットゲート(RG)を通じて電荷保存ノード(FD)をリセットドレイン(RD)に連結された電圧(VDD)にリセット(Reset)させて次のラインセンサ12の電荷の入力を受けることができるようにする。

## [0035]

このように画素部 1 0 を C C D 素子による T D I 方式で構成することによって光量を十分に満足する高分解能の映像を得ることができる。

#### [0036]

また、出力部20の電荷保存ノード(FD)に保存された電荷はCCD素子を通じて移動させるのではなく、増幅器22を通じて増幅した後AD変換器24でデジタル信号に変換してメモリーバッファー26に保存した後出力することによって、CMOS素子によって集積度を向上させることができるだけでなく、少ない電力で転送速度を向上させることができる。

#### [0037]

上述した通り、本発明の実施例によるTDIラインイメージセンサーによれば、CCD素子を通じてTDI(Time Delay Integration)方式で電荷を蓄積するように画素部を構成し、出力部はCCDで蓄積された各コラムの電荷をAD変換してメモリーバッファーに保存した後順次出力するように構成することによって、CCD素子とCMOS素子の特性による解像度と転送速度を向上させるだけでなく消費電力とノイズを低減させることができる。

## [图1]

## (別紙2)

#### (第1欄19~30行)

背景

10

20

25

イメージングデバイスは、多くの用途に役立ちます。特に、遠隔地で動作する機器や、リアルタイム、又は、ほぼリアルタイムで画像データを送信する通信機器の分野では、光子を検知して電気信号を生成することができる光子検出器を含むフォーカルプレーンアレイが開発されている。このようなフォーカルプレーンアレイに使用される様々な技術のうち、電荷結合素子(CCD)は優れた光学性能を持つことが証明されている。そのため、高性能な光子検出器にはCCDセンサがよく取り上げられる。

#### $(第1 欄 3 1 \sim 3 5 行)$

また、航空宇宙用センサの分野では、TDI CCD(時間遅延積分型電荷結合素子)が、センサを横切る画像を走査する、軌道上の動きと組み合わされた加算機能と、ノイズの少ない電荷転送のために、軌道上での観測に非常に適しているとされている。

## (第1欄36~47行)

しかし、CCD は比較的消費電力が大きいという特徴がある。消費電力が気になる機器では、CMOS (Complementary Metal Oxide Semiconductor、原文の「Complimentary」は「Complementary」の誤記と認めた。)デバイスのような他のプロセスで形成されたデバイスが好ましい。特に、CMOS 技術を用いた低消費電力で高密度に実装された処理回路を製造することが要求されるその技術は発達している。しかし、CMOS 光子センサは、CCD に比べてノイズが多く、一般的に光学性能も劣る。また、CMOS 光子センサのみでは、TDI (時間遅延積分)機能を実現す

ることが難しい。

#### $(第1 欄 4 8 \sim 6 0 行)$

そのため、CCD 光子検出器の優れた光学性能と、CMOS プロセスにより可能となる低消費電力及び高密度実装を組み合わせた光子センサの作成が望まれていたのである。しかし、1 枚の基板上で CCD 及び CMOS プロセスを組み合わせることは困難であることが分かった。このような困難は、処理温度や必要な酸化膜の厚さが異なることを含む、両プロセス間の基本的に両立しがたいことから生じる。また、CCD 及び CMOS 両方の技術を用いて単一の基板上に製造されたデバイスは、電荷移動効率の悪さ及びプロセスが最適化されていないことによるノイズの多さのため、不十分な画像品質が問題となる。

#### (第1欄61行~第2欄2行)

両立しがたい製造プロセス技術を統合することをさけるために、第2のプロセスを用いた第2の基板(CMOS 読み出しなど)を相互接続した第1のプロセスを用いた第1の基板(CCD 光子検出器など)に形成された構造を利用するデバイスが開発されてきた。このようなシステムでは、通常、画像を作成するために使用される信号を得るために、検出器(第1)基板から電荷量を検知又は読み取り、次に読み出し及び処理(第2)基板上で電荷を増幅する。

20

25

10

15

#### (第2欄 $3\sim7$ 行)

さらに、電荷の検出は、一般的に、特定の電荷の収集に対して1回だけ実行できることに留意すべきである。また、CCD から増幅されていない信号やバッファされていない信号を供給すると、多くの場合、劣化した信号をもたらすことになる。

#### (第2欄 $9\sim12$ 行)

#### 発明の概要

10

15

20

25

本発明は、これらの問題及びその他の問題と、先行技術の欠点を解決することに向けられている。

#### (第2欄13~28行)

本発明の少なくとも 1 つの実施形態は、列(パラレル)出力において、又は、近くで、CCD からデータを抽出し、その結果、電力を大量に消費するシリアルシフトレジスタを取り除くことにより、CCD の電力損失を劇的に削減することができるという事実に基づいている。このように、列並列電圧出力を持つ CCD 光子検出器と、デジタル化やデータ処理を含む CMOS 読み出し回路を組み合わせることで、現状の技術に比べて大きな利点が得られる。本発明は、個別に製造された電圧出力を有する CCD 光子検出器と CMOS 読み出し回路を、単一の光検出システムに組み合わせることに関するものである。多くの場合、最新の技術を用いて検出器の基板と読み出し回路の基板を機械的及び電気的に結合することになる。なお、列を行と呼んだり、逆に行を列と呼んだりする場合がある。

#### (第2欄29~49行)

本発明の実施形態によれば、センスノードに関連付けられた第1の半導体基板上の電荷結合素子(CCD)光子検出器を含む光子センサシステムが提供される。第1の半導体基板のセンスノードは、第2の半導体基板上の読み出し回路に電気的に相互接続されている。特に、電荷結合素子のセンスノードは、電気的相互接続を介して読み出し回路に電圧信号を提供する。第1の半導体基板は、シリコン又は他の半導体材料で形成された構造を含んでいてもよく、一方、第2の半導体基板は、第1の半導体基板の構造とは異なる半導体構造を含んでいてもよい。本発明の実施形態によれば、電気的接続は、信号ラインを形成してもよく、特定の実

施形態において第3の基板上に形成されてもよいバンプボンド、ワイヤ、ビア、 又はトレースから構成されてもよい。本発明のさらなる実施形態によれば、第1 及び第2の半導体基板は、直接又は第3の基板を介して、互いに機械的に相互接 続されている。

5

10

20

25

## (第2欄50~59行)

第1の半導体基板上の出力ノードとしても知られるセンスノードは、第2の半導体基板上の読み出し回路に信号が伝送される前に、第1又は光子検出器基板上の1又は複数のトランジスタにバッファされてもよい。一例として、1又は複数のトランジスタは、CCD(第1の半導体基板)上に形成されたソースフォロワからなる増幅器を構成する、又はその一部であってもよい。さらに一例として、1又は複数のトランジスタは、CCD上に形成された電圧モード増幅器を構成する、又はその一部であってもよい。

#### 15 (第2欄60行~第3欄3行)

さらに他の実施形態によると、電荷から電圧への増幅器が CCD 上に設けられてもよい。本発明の他の実施形態によれば、センスノードからの電圧信号は、第1の半導体基板上で増幅されることなく、第2の半導体基板上の読み出し回路に渡される。電圧信号を受け取る第2の半導体基板上の読み出し回路は、電圧増幅器、電圧比較器、バッファ、又はアナログデジタル変換器で構成されてもよい。さらに、センスノードの電圧は、相関二重サンプリングの使用を含む、様々な技術を用いて読み取られる。

#### (第3欄4~24行)

本発明の実施形態によれば、光を検知する方法は、第1の半導体基板上に形成された、又は第1の半導体基板からなる CCD を用いて光子を検出することに応答

して電荷を生成することを含んでもよい。さらに、第1の半導体基板は、シリコン半導体で構成されていてもよい。光子の検出に応答して生成された電荷の全部又は一部を含む、第1の電荷パケットとしても知られる第1の収集が、第1のポテンシャルウェルに集められる。その後、第1のポテンシャルウェルに集められた電荷の第1のパケット(収集)に関連する第1の電圧を読み取ることにより、電圧信号が生成される。第1の電圧信号は、第2の半導体基板上に形成された第1の回路コンポーネントに提供され、第1の電圧信号は、第2の半導体基板上の第1の回路コンポーネントを含む回路を用いて処理される。本発明のさらに他の実施形態によれば、第2の電圧信号は、第1のポテンシャルウェルに蓄積した電荷の第1のパケットに関連する第2の電圧を読み取ることにより作成される。すなわち、第1の半導体基板上のポテンシャルウェルに蓄積した電荷の第1のパケットに関連する第2を複数回読み取ることができる。

#### (第6欄50行~第7欄43行)

図6は、本発明の実施形態に係るイメージングセンサアレイ 124 を構成する第1の半導体基板 126 のいくつかの特徴を示す断面図である。図示するように、イメージングセンサアレイ 124 は、半導体基板 126 に形成された複数の画素又は光を検出する手段 604 を含む。さらに、イメージングセンサアレイ 124 は、ノイズ性能を向上させるための読み出し又は合算ウェル 608 と、センスノード(出力ノード)804 とを含む。そのセンスノード(出力ノード)804 から電圧信号が第2の半導体基板 130 に形成された読み出し回路 128(図6 には示されていない)に提供されてもよい。さらに、センスノード804 は、典型的には、フローティングディフュージョンへのコンタクトを有する。他の実施形態では、合算ウェル 608 を採用しなくてもよい。一般的に、そして当業者であれば理解できるように、各画素 604 は、感光領域を構成する。より詳細には、画素 604 に入射する光子に応答して、電荷が蓄積される。さらに、画素 604 の有効な感度範囲内では、蓄積され

た電荷の量は、積分期間中に画素 604 で受け取った光子の数に依存する。また、 当業者であれば理解できるように、図6に図示された画素604は、本発明の実施 形態に係るイメージングセンサアレイ 124 に含まれるエリアアレイ又はサブアレ イ内のリニアアレイ又は1列(又は行)を構成してもよい。したがって、積分期 間の後、収集された電荷は、1つの画素604から直列に次の画素に転送され、最 後に、合算ウェルが採用されていない実施形態では、最後のウェル 614 に転送さ れてもよい。他の実施形態では、電荷は、連続する積分期間中に、連続する画素 604 に蓄積されてもよい。この蓄積された電荷の実質的にすべてが、その後、最 後のウェル 614 に転送される。このプロセスは、当業者には TDI (時間遅延積分) としても知られている。ここでも、ノイズ性能を向上させるために、センスノー ド804 の直前に合算ウェル608 を使用してもよい。図6は、3 相クロッキングを 示しているが、他の実施形態では、4 相又は別の数の相クロッキングを利用して もよい。より詳細には、電荷の各収集が最後のウェル 614 に蓄積されると、読み 出し回路 128(図 6 には示されていない)に伝送される電圧信号 612 を読み出た めに、電荷は最後のウェル 614 からセンスノード 804 に移動させられる。あるい は、第1の半導体基板 126 上に増幅器 (例えば、バッファ又は CTIA (Capacitance Transimpedance Amplifier)) が設けられている実施形態では、電圧信号又は電荷 信号がセンスノード804から読み出され、その後、増幅器の出力によって電圧信 号 612 が供給されてもよい。一般に、画素間の電荷の移動は、転送ゲート 620 を 用いて達成される。最後のゲート(出力ゲート)622 は、センスノードを最後の ウェルから分離するように機能し、又はそれが存在する場合には、最後のゲート 622 は、センスノードを合算ウェルから分離するように機能する。センスノード 804 は、電圧信号 612 に隣接して描かれているが、本発明の実施形態に従って、 中間回路が設けられてもよいことが理解できる。当業者であれば理解できるよう に、中間回路は、センスノード 804 と出力電圧信号 612 との間に介在して、出力 の一部を形成してもよい。さらに、複数のセンスノード804が、画素604の列(行)

10

15

20

25

に関連付けられてもよい。一実施形態では、センスノード804は、CCDの列(行)の両端に存在し、CCDの順方向又は逆方向の動作に使用されてもよい。

#### (第7欄44行~第8欄13行)

10

20

25

図7は、本発明の実施形態に係るハイブリッドイメージャ120のコンポーネン トを模式的に描いたものである。イメージングセンサアレイ 124 の感光領域を構 成する画素 604 の 2 つの列(行) 702a-b が描かれており、各列(行) 702 はセン スノード804 に相互接続されている。第1及び第2の相互接続404a-bは、第1及 び第2のセンスノード804からの電圧信号を、第2の半導体基板130上に形成さ れ、読み出し回路 128 の一部を構成するプリアンプ 708 の入力に供給する。図示 されているように、各センスノード804は、単一のプリアンプ708と関連してい てもよいが、他の配置も可能である。さらに、プリアンプ708は電圧モード増幅 器からなり、相互接続 404a-b によってセンスノード 804 からの電圧信号が供給 されるので、1 つの電荷の収集の複数の測定値を提供するために、センスノード 804 の電圧を複数回読み取ることができる。したがって、信号対雑音比を改善す るために、センスノード804内の、又はセンスノード804に関連する電荷の複数 のサンプル(測定値)を取ることができる。また、1 つ又は複数の追加の増幅器 712 が、読み出し回路 128 の一部として提供されてもよい。図 7 に示されるよう に、そのような追加の増幅器 712 への入力は、1 つ又は複数のプリアンプ 708 か らの出力で構成されてもよい。増幅器 712 が増幅器 708 のいずれかからその入力 を選択的に受け取ることができるように、スイッチ 716 が設けられてもよい。こ の追加の増幅器 712 は、読み出し回路 128 に含まれる少なくとも 1 つの他の増幅 器 708 から入力を受けるので、追加の増幅器 712 は、必ずしも電圧モードの増幅 器でなくてもよい。追加の増幅器 712 からの出力は、次に、処理(例えば相関二 重サンプリング(CDS)及びアナログデジタル変換を含む)、ディスプレイ又はス トレージのために、別の基板又は装置に関連する追加の回路に提供されてもよい。 あるいは、そのような追加回路は、読み出し回路 128 の一部として提供されてもよい。例えば、イメージングセンサアレイ 124 上の画素 604 によって収集された画像データを一時的又は長期的に保存するために、メモリが提供されてもよい。

#### 5 (第8欄14~35行)

10

15

20

25

図8は、本発明の実施形態に従って電圧信号を提供するセンスノード804を含 むハイブリッドイメージャ 124 の一部の概略図である。特に、図示された実施形 態では、センスノード 804 は、ポテンシャルウェル 818 に重なるフローティング ゲート806を構成する。隣接するポテンシャルウェル812からのポテンシャルウ ェル 818 への電荷の転送は、転送ゲート又は CCD ゲートとしても時々知られる制 御ゲート816を使用して制御されてもよい。特に、バイアスゲート822を使用し て、ポテンシャルウェル 818 を空乏状態に設定することができる。画素 604 の 1 つからの画像信号に関連付けられた電荷がポテンシャルウェル 818 に転送される と、ゲート806上の電圧変化が検知され得るように導入される。例えば、フロー ティングゲート806からの電圧信号は、第1の半導体基板126上又は第2の半導 体基板 130 上に形成された増幅器又はプリアンプ 820 に供給されてもよい。検知 された後、信号電荷パケットは、ポテンシャルウェル 818 から転送され、ダイオ ード 830 及びダイオードドレイン 832 を介して除去されてもよいし、あるいは、 ノイズ低減のために複数のサンプルを可能にするためにフローティングゲート 806 の下に残ってもよい。所望の数のサンプルが得られた後、電荷は、ダイオー ドドレイン 832 を介して除去され得る。

#### (第8欄46~60行)

本発明の他の実施形態に従ったハイブリッドイメージャ 124 の部分が、図 9 に示されている。特に、図 9 は、図 8 に描かれたハイブリッドイメージャ 124 と異なっている。センスノード 804 からの電圧信号は、フローティングゲートとして

も機能する電極 904 を使用するために供給される。電極 (ゲート) 904 の電圧は、 リセットトランジスタ 908 によって決定される。また、センスノード 804 から電 圧モードアンプ 820 への電圧信号を運ぶための信号ライン 906 には、リセットス イッチ又はトランジスタ 908 が関連付けられている。リセットスイッチ 908 及び /又は電圧モード増幅器 820 は、第 1 の半導体基板 126 又は第 2 の半導体基板 130 のいずれかに形成されてもよい。検知された後(おそらく複数回)、信号電荷 パケットは、ダイオードドレイン(図 9 には示されていない)を介して除去され 得る。

## (第9欄22~51行)

15

20

25

図 12 は、本発明の実施形態に係るハイブリッドイメージャ 120 の一部を模式 的に示した図である。CCD イメージングセンサアレイ 124 は、複数のサブアレイ 1204 にまとめられた複数の画素 604 を含む。画素 604 の各列(行)は、センスノ ード 804a と関連していてもよい。さらに、サブアレイ 1204 からの双方向の出力 をサポートするために、第 1 のセンスノード 804a が配置されている端部とは反 対側の画素 604 の各列(行)の端部に第2のセンスノード 804b が設けられても よい。図示されているように、第1の半導体基板126上に形成された増幅器1208 は、各センスノード804に関連していてもよい。図面を明確にするために、画素 のすべての列(行)が、関連付けられたセンスノード804又は増幅器1208、又は 図に関連して説明される他のコンポーネントと一緒に示されているわけではな い。当業者であれば理解できるように、増幅器 1208 は、センスノード 804 から検 知された電圧と異なる出力電圧、又は比較するために増幅された出力電圧を提供 する必要はない。したがって、電圧バッファされた出力を提供するために、増幅 器 1208 は、ソースフォロワ又は他のバッファを構成してもよい。本発明の他の実 施形態によれば、増幅器 1208 は、関連するセンスノード 804 から電荷信号を読み 取り、増幅器の出力として電圧信号を提供してもよい。したがって、CCD イメー

ジングセンサアレイ 124 を構成する第1の半導体基板 126 上で、電荷から電圧への変換が行われてもよい。あるいは、CCD 撮像素子を構成する第1の半導体基板 126 上の増幅器 1208 を省略してもよく、その場合は各センスノード 804 から直接 電圧信号を読み出す。

5

10

15

20

25

## (第9欄52行~第10欄12行)

センスノード804からの電圧信号は、センスノード804の増幅されていない電 荷の収集から読み取られたものであっても、第 1 の半導体基板 126 上の増幅器 1208 の出力から読み取られたものであっても、相互接続 404 によって第 2 の半導 体基板 130 上に形成された読み出し回路 128 に提供される。例えば、第1の半導 体基板 126 上の CCD イメージングセンサアレイ 124 の画素 604 からの電圧信号 は、第2の半導体基板130上に形成された読み出し回路128の少なくとも一部を 構成する電圧モードの増幅器又はプリアンプ708の入力に伝達される。増幅器708 は、図示された例では、その図において第1の半導体基板126の下にある第2の 半導体基板 130 の一部に配置されているため、図 12 に点線を用いて示されてい る。当業者であれば理解できるように、電圧モード増幅器は、高い入力インピー ダンス又は本質的に無限大の入力インピーダンスによって特徴付けられる。その 結果、相互接続 404 によって増幅器 708 の入力に伝達されるようなセンスノード 804 の電圧は、複数回サンプリング又は読み取ることができる。これは、センス ノード804に直接接続された場合、センスノード804に収集された電荷を消耗し、 したがって、センスノード804から一度だけ読み取ることができるチャージモー ドアンプとは対照的である。また、当業者であれば理解できるように、増幅器708 は、入力電圧と異なる、又は入力電圧と比較するために増幅された出力電圧を提 供する必要はない。例えば、増幅器 708 は、ソースフォロワ又は他のバッファで 構成されてもよい。

## (第10欄13~20行)

図 12 に示されているように、第 1 の半導体基板 126 は、ポテンシャル障壁を 形成するための多数の手段、又は制御ゲート 816 を含んでもよい。当業者であれ ば理解できるように、制御ゲート 816 は、収集された電荷を画素 604 から、又は 画素 604 の列(行)から順次、センスノード 804 に移動させるために設けられて もよい。また、関連するセンスノード 804 をリセットするために、リセットスイ ッチ 908 を第 1 の半導体基板 126 上に形成することができる。

## (第10欄21~57行)

10

15

20

25

前述のように、第2の半導体基板130上に形成された読み出し回路128は、増 幅器又はプリアンプ708を含んでいてもよい。また、代替的又は追加的に、読み 出し回路 128 は、1/f ノイズを含む低周波ノイズ成分を低減するために CDS 回路 1000 を含んでいてもよい。双方向出力が提供される場合、画素 604 又は画素の列 (行)に含まれる画素 604 に対する電圧信号が得られるセンスノード 804 は、第 2の半導体基板 130 に形成されたスイッチ 1212 を用いて選択されてもよい。追加 の増幅は、列(行)増幅器 1216 によって提供されてもよい。これらの増幅器 1216 は、差動増幅器又はシングルエンド増幅器で構成されてもよい。本発明の実施形 態によれば、画素からの信号又は TDI 配置の多数の画素からの統合された信号は、 次に、アナログデジタル変換器(ADC)1220 によって処理される。例として、ADC は、ランプ ADC 又はパイプライン ADC で構成されてもよい。データが ADC によっ てデジタル化された後、同じく第2の半導体基板130上に形成されたシリアライ ザ1224によってデジタル処理され得る。その後、シリアライザからの出力は、第 2 の半導体基板 130 から、例えばストレージやディスプレイのために、他の回路 に渡すことができる。 デジタルデータの転送は、 デジタルデータリンク 1228 によ るものであってもよい。例えば、デジタルデータリンク 1228 は、LVDS (Low Voltage Differential Signaling) リンクで構成されていてもよい。クロック生成は、第

2の半導体基板 130 上の読み出し回路 128 の一部として設けられたクロック生成 回路 1232 によって行われてもよい。本発明の実施形態によれば、外部回路 1236、 又は、第1の半導体基板 126 又は第2の半導体基板 130 のいずれにも形成されて いない回路を使用して、クロック信号を正しい電圧で CCD 検出アレイ 124 に結合してもよい。他の実施形態では、外部回路 1236 も第2の半導体基板 130 上に形成されてもよい。多数の回路が第2の半導体基板 130 上又はその一部に形成されていると説明してきたが、これらの回路の一部又は全部を省略したり、他の基板に形成したりしてもよい。

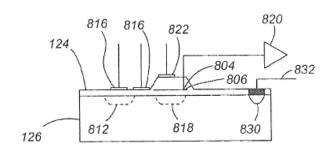

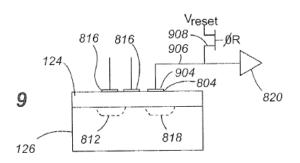

#### 10 図8

図 9

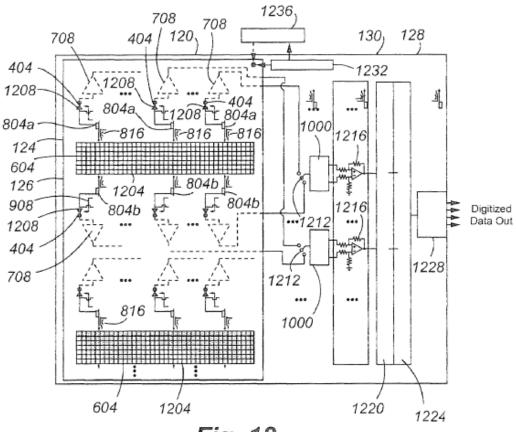

Fig. 12

#### (別紙3)

10

15

20

25

- 1 特開平2-159737号公報(乙5)

- (1) 「〔従来の技術〕

固体撮像装置で検出した映像信号から各種色信号や輝度信号等を形成するために電荷転送デバイスより成るCCD遅延線が使用され、信号電荷の転送効率等の点で埋込チャンネルCCDが用いられている。」(1頁右下欄3~8行)

- (2) 「次に第10図に示す第3の従来例はフローティング・ゲート型アンプと呼ばれ、特開昭63-88864号公報等に開示されている。原理を概略的に説明すると、第10図において、BCCD1の終端に所定の直流電圧OGが印加されるゲート電極4、フローティング・ゲート5、リセット用ゲート電極6、7及びドレインDが順番に形成され、ドレイン端子は昇圧回路3の定電圧 $V_{DD}$ が印加され、リセット用ゲート電極6.7は所定タイミングのリセット信号 $\phi_R$ に同期してオンとなることによりフローティング・ゲート5下の信号電荷をドレインDへ排出する。 $Q_1$ は電源電圧 $V_{CC}$ とフローティング・ゲート5との間に接続するリセット用トランジスタであり、所定タイミングのリセット信号RSTに同期してオンとなることによりフローティング・ゲート5を電圧 $V_{CC}$ に等しい電位にリセットする。」(2頁右下欄4~20行)

- (3) 「[実施例]

以下本発明の一実施例を図面と共に説明する。

第1図はCCD遅延線本体の終端部分の構造と信号出力手段を示す実施例構成図であり、第2図及び第3図は信号出力手段の詳細な回路構成を示す。

第1図において、P形半導体基板10の表面部分にN<sup>-</sup>形不純物のイオン注 入層11が形成され、更にゲート酸化膜を介して電荷転送用のゲート電極が積 層されることで同図中の領域Aに埋込チャネルCCD(BCCD)が形成され、 該領域Aは遅延素子の本体部分を構成している。 (中略)

10

15

20

次に、信号出力手段の構成を説明するに、20はフローティング・ゲート17に生じる電圧を検出するポテンシャル検出回路であり、第2図に示すボルテージ・フォロワ型回路または第3図に示すようなスイッチト・キャパシタ積分器を備えた回路から形成されている。

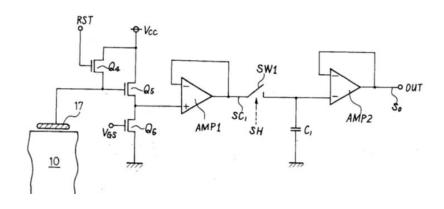

即ち、第2図に示す回路にあっては、フローティング・ゲート17にゲート接点が接続すると共にソース接点が電源端子 $V_c$ 。に接続するMOS型トランジスタ $Q_s$ 、ゲート接点にリセット信号RSTが印加されることにより該ゲート接点と電源端子 $V_c$ 。間を開閉するように接続されたMOS型トランジスタ $Q_6$ 、トランジスタ $Q_5$ のドレイン接点にソース接点が接続すると共にドレイン接点がアース端子に接続し且つゲート接点に所定のバイアス電圧 $V_{GS}$ が印加されるMOS型トランジスタ $Q_6$ を備え、更にトランジスタ $Q_5$ のドレイン接点がバッファ・アンプAMP1を介してアナログ・スイッチSW1に接続し、アナログ・スイッチSW1の出力接点が容量素子 $C_1$ を介してアース端子に接続すると共に、バッファ・アンプAMP2を介して出力端子OUTに接続している。

ここで、リセット信号RSTは所定のタイミングでフローティング・ゲート 17を電源端子 $V_c$ の電位にリセットするためにあり、アナログ・スイッチSW1はサンプル・ホールド信号SHに同期して開閉動作することにより容量素子 $C_1$ にフローティング・ゲート17の電圧をサンプル・ホールドさせ、更に、容量素子 $C_1$ に保持された電圧をバッファ・アンプAMP2を介して出力端子OUTに発生させることにより、フローティング・ゲート17に生じたポテンシャルの変化を電圧の変化として出力させる。」(4頁左上欄3行~左下欄16行)

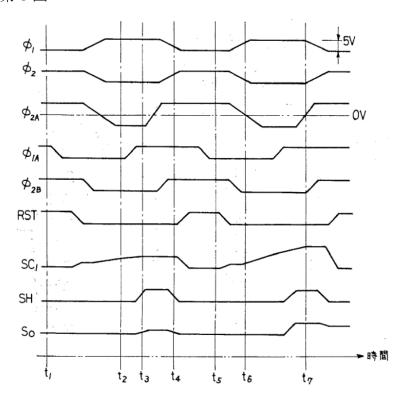

25 (4) 「 次にかかる構成の実施例の作動を第5図のタイミング・チャート及び第6図のポテンシャル・プロフィールに基づいて説明する。尚、第6図は第1図

の構造説明図に対応し且つ第5図の適宜の時点におけるポテンシャル・プロフィールを示す。

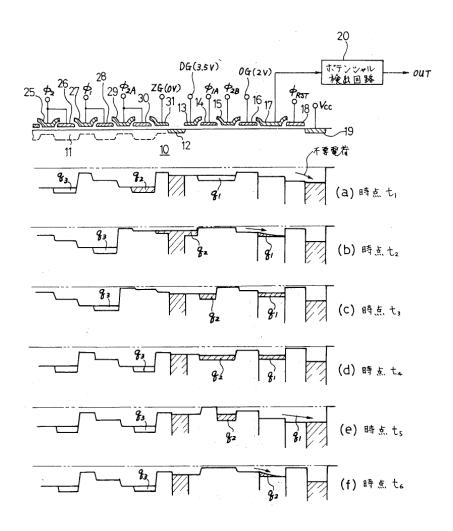

尚、この初期化の時点  $t_1$ では第6図(a)に示すように、最も出力側に位置する信号電荷  $q_1$ がゲート電極 1 4 、 1 5 下に転送され、次の信号電荷  $q_2$ がゲート電極 3 0 下に転送され、次の信号電荷  $q_3$ がゲート電極 2 6 下に転送される関係になる。

次に、時点  $t_2$ において、クロック信号 $\phi_{1A}$ 及び $\phi_{2B}$ が "L" レベル、クロック信号 $\phi_{2A}$ がマイナスの "L" レベルとなることにより、第6図(b)に示すように、ゲート電極 29、30、14、15 下のポテンシャルが浅くなるので、信号電荷  $q_1$ がゲート電極 16 下のポテンシャル障壁を越えてフローティング・ゲート 17 下へ転送されると共に、信号電荷  $q_2$ がゲート電極 31、13 及び不純物層 12 下に転送される。その結果、フローティング・ゲート 17 の電位が信号電荷  $q_1$ に比例して変化し、第2図の回路の場合にはこのフローテ

ィング・ゲート 1 7 の電位に相当する電圧信号 S  $C_1$  がバッファ・アンプ A M P 1 の出力接点に発生し、第 3 図の回路の場合にはフローティング・ゲート 1 7 の電位に相当する電圧が容量素子  $C_3$  に保持されると同時に差動増幅器 A M P 3 の出力接点に該保持電圧に等しい電圧信号 S  $C_1$  が発生する。

次に、時点  $t_3$ において、クロック信号  $\phi_{1A}$ が "H" レベルとなることによりゲート電極 1 4 下に信号電荷  $q_2$ が転送され、更に時点  $t_4$ においてクロツク信号  $\phi_{2B}$ が "H" レベルとなることによりゲート電極 1 5 下へも信号電荷  $q_2$  を転送すると同時に、クロツク信号  $\phi_1$ 、 $\phi_2$ に同期してBCCDより転送されてくる次の 1 ピクセル分の信号電荷  $q_3$ をゲート電極 2 9、 3 0 下へ転送する。

更に時点  $t_3 \sim t_4$ の間でサンプル・ホールド信号 S Hが"H"レベルとなることで、第2図の回路にあっては出力信号 S  $C_1$  を容量素子  $C_1$  に保持させ、第3図の回路にあっては出力信号 S  $C_1$  を容量素子  $C_3$  に保持させ、そして夫々の回路とも該保持電圧に比例した信号  $S_0$  を出力端子 O U T に発生させる。

10

15

20

25

このようにゲート電極 14、15 下まで転送されている信号電荷  $q_1$ の読出しは上記時点  $t_1 \sim t_4$ の処理で完了する。

次に、時点  $t_5$ において、リセット信号RSTを"H"レベルにすると共に制御信号 $\phi_{RST}$ を"H"レベルにすることによって、第6図(d)に示すように、ゲート電極 1 8 下のポテンシャル障壁の高さを下げると同時にフローティング・ゲート 1 7 下のポテンシャルを所定の初期レベルに設定して信号電荷  $q_1$  を不純物層 1 9 へ廃棄し、第6図(a)に示したのと同様に初期化が行われる。

更に時点  $t_5$ では信号  $\phi_{1A}$  を "L" レベルにすることにより信号電荷  $q_2$  をゲート電極 1 5 下へのみ移し、更に時点  $t_6$  において信号  $\phi_{2B}$  を "L" レベルとすることにより信号電荷  $q_2$  をフローティング・ゲート 1 7 下へ転送する。

そして、時点  $t_6$ においてフローティング・ゲート 1 7 へ転送された信号電荷  $q_2$ が上記信号電荷  $q_1$ と同様に検出され、該信号電荷  $q_2$ に相当する電圧信号  $s_0$ が出力される。このようにして信号電荷  $q_2$ の読取り処理が完了する。

尚、時点  $t_1$ においてゲート電極 2 6 下に在った信号電荷  $q_3$ は時点  $t_1 \sim t_6$ の期間中にゲート電極 3 0 下まで転送され上記同様の読出し処理がなされる。このような作動はB C C D のクロック信号  $\phi_1$ 、 $\phi_2$  の周期に同期して繰り返され、遅延した 1 ステージ毎の信号を出力することができる。」(5 頁右下欄 5 行  $\sim$  6 頁右下欄 1 8 行)」

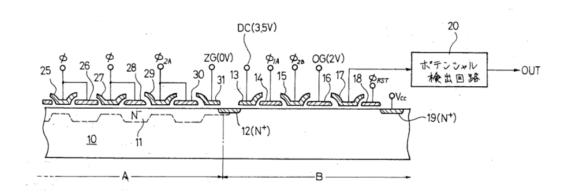

## (5) 第1図

第2図

10

第5図

## 第6図

2 特開平7-161969号公報(乙6)

## 5 [0002]

10

【従来の技術】CCDにおいては信号電荷を低雑音検出及び増幅することが要求される。CCDの電荷検出装置の代表的なものとしては、フローティング・ディフュージョン・アンプ (Floating Diffusion Amplifier 以下FDAと略記)とフローティング・ゲート・アンプ (Floating Gate Amplifier 以下FGAと略記)があった。FDAは最も普及しているものであり、図9にFDAを用い

た従来のCCD装置の全体構成を示す。フォトダイオード(PD)90に入射した光子は、電荷に変換されPD90内に蓄積される。一定時間後、信号電荷はVCCD91に読み出され、HCCD92を経てFDA93に入力され、電圧として検出される。このようなFDAでは、リセット雑音が発生するという問題があった。一方FGAには、非破壊でリセット雑音のない増幅器を実現可能であるという特徴があった。

【0004】図10は従来のFGAの寄生容量を示す図であり、フローティング ゲート(FG)95下に信号電荷Qが入力した場合の断面の形状を示している。 Si 基板上にゲート酸化膜 96をはさんで、ポリシリコンによってFG95が形成 される。SiO2で絶縁膜を形成後、アルミニウムやタングステンによってバイア スゲート 94 が形成される。この時C1は信号電荷QとFG95間容量、C2は FG95とBG94間容量、C3は信号電荷QとP型基板間の空乏層容量、C4は FG95とP+領域(チャンネル・ストッパとして機能)間容量、C5はMOSトランジスタ(以下Trと略記)の入力容量である。MOSTrはソースフォロワ(図示せず)を構成し、信号電圧を低出力インピーダンスに変換して出力する。つまりFG95は電荷検出用ゲートと初段Trのゲートを兼ねたことになる。このような寄生容量が存在した状態で、FG95下に信号電荷Qが入力された場合、FG95には(1)式にしたがって $\Delta$ Vだけの電圧変化が現れる。

【0007】図11は従来のFGA周辺の平面図と断面図であり、HCCD92上に形成されたゲートに $\phi$ H1、 $\phi$ H2が印加されることにより信号電荷が転送される。信号電荷は、アウトプットゲート(OG)97を越えてFG95下に転送され、電荷電圧変換が行われる。FG95で検出された信号電荷Qは、FDAと同様に、リセットゲート(RG)98によって、リセットドレイン(RD)99に排出される。図11より明らかなように、FG95とOG97、RG98がオーバーラップしている。これは $\phi$ H1、 $\phi$ H2が印加されたゲートと同様に、FG95を配置したためであり、FG95とOG97間にC6、FG95とRG98間にC7

の容量が新たに付加されている。したがって従来では、FGAの感度はFDAに比較して $4\sim5$ 割低くなっていた。

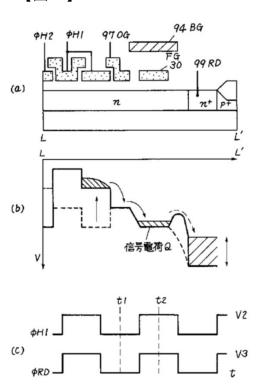

【0032】次に、本発明の第5の実施例について、図面を参照しながら説明する。図5は本発明の第5の実施例におけるFGA周辺の断面図、ポテンシャル図とタイミングチャートである。第5の実施例の特徴は、リセットゲートを形成せず、リセットドレインに $\phi$ H1と同相のパルスを印加することでリセット動作を行うことにある。図5(a)は断面図であり、リセットゲートを取り除いた構成になっている。FG30とRD99間には間隙が存在し、BG94もこの間隙を覆いつくしてはいない。この状態でのポテンシャル図が図5(b)であり、RD99にローレベルの駆動信号(ゼロではない)が印加された場合、FG30とRD99間にはポテンシャルギャップが存在する。

10

15

20

25

- 【0033】図5(c)はタイミングチャートであり、 $\phi$ H1、 $\phi$ RD(リセットドレインに印加する信号)の関係を示している。図5(b)ではt1での状態を実線で、t2での状態を破線で示している。t2にてハイレベル信号(V3)が加えられるためポテンシャルギャップが消滅し、既に(t1)FG30下に転送されてきた信号電荷QはRD99に吸収される(リセットされる)。この時 $\phi$ H1、 $\phi$ RDは同相であるが、駆動信号のハイレベル(V2、V3)は異なっている。従来のリセットパルス幅は、 $\phi$ H1のハイ期間の半分程度にする必要があったが、第5の実施例では $\phi$ H1と同等でよいため駆動回路が簡単になる。またリセットゲートが存在しないため、余分な寄生容量を削減でき電荷検出感度も向上する。なお第5の実施例をFDAに適用しても同様の効果が得られるのは言うまでもない。

- 【0034】次に、本発明の第6の実施例について、図面を参照しながら説明する。図6は本発明の第6の実施例におけるFGA周辺の断面図、ポテンシャル図とタイミングチャートである。第6の実施例の特徴は、OG97に隣接する ΦH1L(HCCDの最終ゲート)に印加する信号振幅を、他の ΦH1に印加す

る信号振幅より大きくすることにある。

【0035】図6(a)は断面図であるが、 $\phi$ H1の最終段のみに別信号を加える構成とすることが従来と異なる。図6(c)はタイミングチャートであり、図6(a)に示す構成の電荷検出装置に供給する信号である。また図6(b)はこの時のポテンシャル図である。 $\phi$ H1、 $\phi$ H2には信号振幅がV4となるパルスを印加し、 $\phi$ H1Lには信号振幅V5なるパルスが印加される(V4<V5)。 $\phi$ H1Lの信号振幅が大であるため、OG97電位を従来より低く設定してもCCDは動作可能である。したがってBG94、FG30の電位を下げても動作可能であるため、リーク電流の発生は大幅に抑制され、FG電位の変動もほとんどなくなる。なお第6の実施例をFDAに適用しても動作可能なことは言うまでもない。

## 【図5】

15

10

## 【図6】

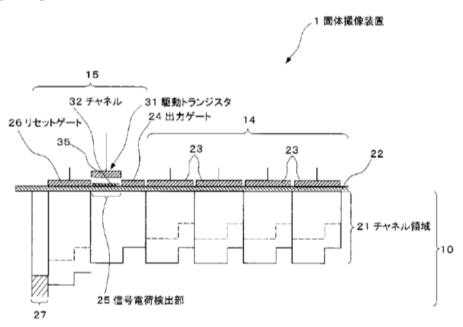

3 特開2008-60097号公報(乙7)

#### [0003]

10

FD以外の主要な電荷検出方式としてフローティングゲート(以下FGという、FDはFloating Gate の略)方式がある。FG方式は主にCCD素子の電荷検出部として用いられていて、例えばCCD撮像素子の水平CCD終端部において、ある電位にリセットされた電荷検出用フローティングゲート(Floating Gate)下のCCDチャネルに信号電荷を転送することで、信号電荷量に応じてFG電位が変化し、このFGが出力MOSFET(FET: Field Effect Transistor)のゲートに接続された構造をなしており、出力MOSFETのチャネル電流が信号量に応じて変調されることを原理としている。本方式ではFG部リセット用トランジスタが接続されていることやFG部面積の関係から、上記FD方式にくらべ電荷検出容量が大きくなり易く、高変換効率の電荷検出部を得られにくい。しか

しながら後段の出力部動作電圧を低く設定し易いことや非破壊読み出しであることから複数個のFGを並べて検出回路のSNを向上させる手段をとれる等のメリットがある。

#### [0013]

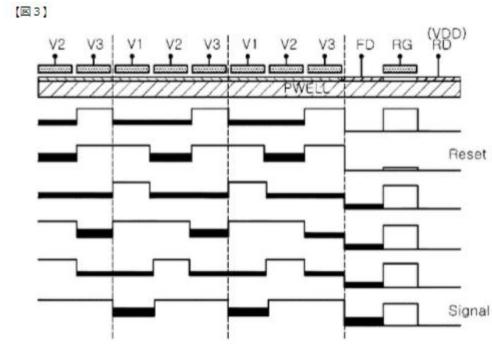

まず、固体撮像装置の概要を、CCD型固体撮像装置を一例として説明する。 図3に示すように、固体撮像装置(CCD型固体撮像装置)1は、入射光を光電 変換する光電変換部11と、光電変換部11で光電変換して得られた電荷を垂直 転送する垂直転送部12とを備えたイメージ部13と、垂直転送された信号電荷 を出力側に水平転送する水平転送部14と、水平転送部24より出力された信号 電荷を電圧に変換し増幅する出力部15が備えられている。

#### [0014]

10

15

上記出力部15の詳細は、図1および図2に示すように、半導体基板10には、水平転送部(例えば水平転送CCD)14が形成されている。この水平転送部14は、半導体基板10に形成されたチャネル領域21上に絶縁膜22を介して転送ゲート23が配列された構成となっており、各転送ゲート23が図示はしないが各垂直転送部に接続されている。上記水平転送部の出力側の半導体基板10上には上記絶縁膜22を介して出力ゲート(水平出力ゲート)24、信号電荷検出部25、リセットゲート26が順に形成されている。上記信号電荷検出部25は、例えば駆動トランジスタ31で構成されている。

#### $\begin{bmatrix} 0 & 0 & 1 & 7 \end{bmatrix}$

また、上記リセットゲート26は、上記コントロールゲート35の信号電荷の進行方向側に間隔を配して設置されていることになる。上記リセットゲート26の上記駆動トランジスタ31とは反対側の上記半導体基板10には、リセットドレイン27が形成されている。

#### [0018]

上記固体撮像装置1では、水平転送部14を転送された信号電荷は水平出力ゲ

ート24下のチャネル領域21を通って、コントロールゲート35下のチャネル領域21に転送されると、信号電荷量に応じた電位変化が同チャネル領域21に生ずる。このチャネル領域21に生じた電位変化が容量結合で駆動トランジスタ31のチャネル32の電位を変調する。上記駆動トランジスタ31の電流-電圧(I-V)特性はMOSFETの電流-電圧(I-V)特性と同様なる傾向を示す。したがって、チャネル領域21が駆動トランジスタ31のゲート電極部として機能する。よって、駆動トランジスタ31を流れる電流が変調を受けて信号電圧に変換されて、ソースフォロワを通して、信号出力として外部に出力される。

#### $[0\ 0\ 1\ 9]$

10

20

本実施例では、信号電荷を読み出した後に、リセットゲート26をHighにして、チャネル領域21からリセットドレイン27に電荷の吐き出しを行う。このリセット動作において、コントロールゲート35に対してLow側に電位を与え、チャネル領域21の電位を浅くし、チャネル領域21からリセットゲート26への完全転送を助長する動作とすることもできる。

#### [0020]

上記固体撮像装置1では、信号電荷検出部25が水平転送部14と水平出力ゲート24を介して連続して形成され、信号電荷検出部25からリセットゲート26への電荷転送がCCD転送(完全転送)で行われる。そのためKTCノイズやチャージシェアリング(Charge sharing)ノイズを持たないため、高感度化が可能になる。また、上記固体撮像装置1は、基本的にはFG方式の固体撮像装置の一種であるものの、FG方式以上の高変換利得を得ることが可能である。

# 【図1】

## 【図3】