令和3年3月23日判決言渡 同日原本交付 裁判所書記官 令和2年(ワ)第6675号 特許権侵害行為差止等請求事件 口頭弁論終結日 令和3年1月26日

判

5

10

15

20

原 告 合同会社IP Bridge1号

上記訴訟代理人弁護士

酒

迎

明

洋

上記訴訟代理人弁理士

石

橋

克

之

被 告 マイクロンジャパン株式会社

上記訴訟代理人弁護士岩瀬ひとみ同紋谷崇俊同草深充彦

主

- 1 原告の請求をいずれも棄却する。

- 2 訴訟費用は原告の負担とする。

事実及び理由

# 第1 請求

- 1 被告は、別紙被告製品目録記載の各製品を輸入し、譲渡し、譲渡の申出をしてはならない。

- 2 被告は、別紙被告製品目録記載の各製品を廃棄せよ。

- 25 3 被告は、原告に対し、1億円及びこれに対する令和2年3月20日(訴状送達の日の翌日)から支払済みまで年5分の割合による金員を支払え。

### 第2 事案の概要等

1 事案の概要

10

15

25

本件は、発明の名称を「半導体集積回路装置及びその製造方法」とする特許権 (特許第3593079号。以下、「本件特許権」といい、この特許を「本件特許」 といい、その特許出願の願書に添付された明細書及び図面を併せて「本件明細書」 という。)の特許権者である原告が、被告が輸入、譲渡している別紙被告製品目録 記載の製品(以下、これらを「被告製品」と総称する。)は本件特許の請求項1ないし3、請求項5ないし8の発明の各技術的範囲に属するものであると主張して、被告に対し、特許法100条1項及び2項に基づき被告製品の輸入、譲渡等の差止め及び廃棄を求めるとともに、主位的に民法709条に基づき損害賠償金(一部請求)及び遅延損害金の支払を、予備的に民法703条に基づき不当利得金(一部請求)及び遅延利息の支払を求める事案である。

- 2 前提事実(争いがない事実については証拠番号を付さない。以下同じ。)

- (1) 原告は、知的財産権の取得、保有、管理、使用・実施の許諾及び売買並びにこれらの斡旋及び仲介等を業とする合同会社である。(弁論の全趣旨)

被告は、半導体装置、集積回路、半導体装置・集積回路の組合せ製品(非特注商品及び特注製品を含む。)、それらの装置、回路、部品、付属品、構成品及び材料の販売、それらの製品の販売代理及びそれに関連する輪入等を業とする株式会社である。

(2) 原告は、以下の本件特許権を有している。

ア 特許番号 特許第3593079号

イ 発明の名称 半導体集積回路装置及びその製造方法

ウ 出願日 平成13年9月27日

工 優先日 平成12年10月2日

才 登録日 平成16年9月3日

### (3) 請求項1について

10

15

20

25

ア 本件特許権の特許請求の範囲の請求項1の発明(以下「本件発明1」という。)は、以下のとおりである。

「ライン状パターンを有する回路パターンを備えた半導体集積回路装置であって、前記回路パターンはメモリ回路のライン状パターンであるメモリ用ライン状パターンを含み、前記回路パターンの配置領域の内部にダミーパターンが挿入されており、前記メモリ用ライン状パターンを含む前記ライン状パターンの総周縁長と前記ダミーパターンの総周縁長との合計を前記回路パターンの配置領域の面積により除することによって得られた第1の単位面積当たりの周縁長が、前記メモリ用ライン状パターンの総周縁長を前記メモリ回路が形成されている領域の面積により除することによって得られた第2の単位面積当たりの周縁長以下となるように設定されていることを特徴とする半導体集積回路装置。」

- イ 本件発明1を分説すると,以下のとおりである(以下,各構成について「構成要件1A」などと表記する。以下同じ。)。

- 1 A ライン状パターンを有する回路パターンを備えた半導体集積回路装置であって,

- 1 B 前記回路パターンはメモリ回路のライン状パターンであるメモリ用 ライン状パターンを含み,

- 1 C 前記回路パターンの配置領域の内部にダミーパターンが挿入されて おり,

- 1D 前記メモリ用ライン状パターンを含む前記ライン状パターンの総周 縁長と前記ダミーパターンの総周縁長との合計を前記回路パターンの 配置領域の面積により除することによって得られた第1の単位面積当 たりの周縁長が,前記メモリ用ライン状パターンの総周縁長を前記メモ リ回路が形成されている領域の面積により除することによって得られ

た第2の単位面積当たりの周縁長以下となるように設定されていること

1 E を特徴とする半導体集積回路装置。

### (4) 請求項2について

ア 本件特許権の特許請求の範囲の請求項2の発明(以下「本件発明2」という。)は、以下のとおりである。

「前記ダミーパターン及び前記メモリ用ライン状パターンを含む前記ライン状パターンは同一の異方性ドライエッチング工程によって形成されていることを特徴とする請求項1に記載の半導体集積回路装置。」

イ 本件発明2を分説すると、以下のとおりである。

- 2 A 前記ダミーパターン及び前記メモリ用ライン状パターンを含む前記 ライン状パターンは同一の異方性ドライエッチング工程によって形成 されていること

- 2B を特徴とする請求項1に記載の半導体集積回路装置。

## 15 (5) 請求項3について

10

20

25

ア 本件特許権の特許請求の範囲の請求項3の発明(以下「本件発明3」とい う。)は、以下のとおりである。

「前記第1の単位面積当たりの周縁長が、前記第2の単位面積当たりの周縁長の70%以上で且つ100%以下の範囲に設定されるように、前記ダミーパターンが挿入されていることを特徴とする請求項1又は2に記載の半導体集積回路装置。」

- イ 本件発明3を分説すると、以下のとおりである。

- 3A 前記第1の単位面積当たりの周縁長が、前記第2の単位面積当たりの 周縁長の70%以上で且つ100%以下の範囲に設定されるように、前 記ダミーパターンが挿入されていること

- 3 B を特徴とする請求項1又は2に記載の半導体集積回路装置。

### (6) 請求項5について

10

15

20

25

ア 本件特許権の特許請求の範囲の請求項5の発明(以下「本件発明5」という。)は、以下のとおりである。

「繰り返しパターンを有する素子群の形成領域に配置されており且つ第 1のライン状パターンを有する第1の回路パターンと、前記素子群以外の他の部分の形成領域に配置されており且つ第2のライン状パターンを有する第2の回路パターンとを備えた半導体集積回路装置であって、前記第1のライン状パターンの総周縁長を前記第1の回路パターンの配置領域の面積により除することによって得られた第1の単位面積当たりの周縁長は、前記第2のライン状パターンの総周縁長を前記第2の回路パターンの配置領域の面積により除することによって得られた第2の単位面積当たりの周縁長よりも大きく、前記第2の回路パターンの配置領域の内部にダミーパターンが、前記第1のライン状パターンの総周縁長と前記第2のライン状パターンの総周縁長と前記第2のライン状パターンの総周縁長と前記第1の回路パターンの配置領域の面積と前記第2の回路パターンの配置領域の面積との合計により除することによって得られた第3の単位面積当たりの周縁長が、前記第1の単位面積当たりの周縁長以下になるように挿入されていることを特徴とする半導体集積回路装置。」

- イ 本件発明5を分説すると、以下のとおりである。

- 5 A 繰り返しパターンを有する素子群の形成領域に配置されており且つ 第1のライン状パターンを有する第1の回路パターンと,

- 5 B 前記素子群以外の他の部分の形成領域に配置されており且つ第2の ライン状パターンを有する第2の回路パターンとを備えた半導体集積 回路装置であって、

- 5 C 前記第1のライン状パターンの総周縁長を前記第1の回路パターンの配置領域の面積により除することによって得られた第1の単位面積

当たりの周縁長は、前記第2のライン状パターンの総周縁長を前記第2 の回路パターンの配置領域の面積により除することによって得られた 第2の単位面積当たりの周縁長よりも大きく、

- 5 D 前記第2の回路パターンの配置領域の内部にダミーパターンが,前記第1のライン状パターンの総周縁長と前記第2のライン状パターンの総周縁長と前記第1の回路 総周縁長と前記ダミーパターンの総周縁長との合計を前記第1の回路 パターンの配置領域の面積と前記第2の回路パターンの配置領域の面積との合計により除することによって得られた第3の単位面積当たり の周縁長が,前記第1の単位面積当たりの周縁長以下になるように挿入されていること

- 5 E を特徴とする半導体集積回路装置。

- (7) 請求項6について

10

15

20

25

ア 本件特許権の特許請求の範囲の請求項6の発明(以下「本件発明6」という。)は、以下のとおりである。

「前記ダミーパターン,前記第1のライン状パターン及び前記第2のライン状パターンは同一の異方性ドライエッチング工程によって形成されていることを特徴とする請求項5に記載の半導体集積回路装置。」

- イ 本件発明6を分説すると、以下のとおりである。

- 6 A 前記ダミーパターン,前記第1のライン状パターン及び前記第2のライン状パターンは同一の異方性ドライエッチング工程によって形成されていること

- 6 B を特徴とする請求項5に記載の半導体集積回路装置。

- (8) 請求項7について

- ア 本件特許権の特許請求の範囲の請求項7の発明(以下「本件発明7」という。)は、以下のとおりである。

「前記第3の単位面積当たりの周縁長が、前記第1の単位面積当たりの周

縁長の70%以上で且つ100%以下の範囲に設定されるように,前記ダミーパターンが挿入されていることを特徴とする請求項5又は6に記載の半導体集積回路装置。|

- イ 本件発明7を分説すると、以下のとおりである。

- 7A 前記第3の単位面積当たりの周縁長が、前記第1の単位面積当たりの 周縁長の70%以上で且つ100%以下の範囲に設定されるように、前 記ダミーパターンが挿入されていること

- 7B を特徴とする請求項5又は6に記載の半導体集積回路装置。

- (9) 請求項8について

10

15

20

25

ア 本件特許権の特許請求の範囲の請求項8の発明(以下「本件発明8」という。)は、以下のとおりである。

「前記素子群はメモリであることを特徴とする請求項5~7のいずれか1項に記載の半導体集積回路装置。」

- イ 本件発明8を分説すると、以下のとおりである。

- 8A 前記素子群はメモリであること

- 8 B を特徴とする請求項5~7のいずれか1項に記載の半導体集積回路 装置。

- (10) 原告は、被告製品について、半田ボールを有するパッケージ基板と、パッケージ基板の中央に搭載された半導体チップとからなり、以下の構成を有するものであると主張する。

- a 矩形の平面視形状を有する半導体チップを有し、半導体チップ上の面積 4 7, 778,  $500 \mu m^2$ の領域に回路パターンが形成されており、

- b 半導体基板上に形成されるゲート電極を含む階層において,互いに異なる 回路パターンを有するメモリセル領域,センスアンプ領域,ロウ・デコーダ 一領域,選択・制御回路領域,ロジック領域,アナログ領域,I/O領域を 含み,

- c メモリセル領域は総面積30,940,299.52 $\mu$ m<sup>2</sup>であり,ライン 状のビットラインを含み,その周縁長の合計は1,105,115,878.4 $\mu$ mであり,

- d センスアンプ領域,ロウ・デコーダー領域,選択・制御回路領域,ロジック領域,アナログ領域,I/O領域の各領域の回路パターンはライン状のゲート電極とダミーゲートを含み、

- e センスアンプ領域は総面積6,805,217.28 μm²であり,当該領域のゲート電極の周縁長の合計は61,804,093.44 μmであり,ダミーゲートの周縁長の合計は515,604.48 μmであり,

- f ロウ・デコーダー領域は総面積2,455,826.60 μm²であり,当 該領域のゲート電極の周縁長の合計は15,625,846.40 μmであり, ダミーゲートの周縁長の合計は3,580,464.00 μmであり,

- g 選択・制御回路領域は総面積623,132.16 μm²であり,当該領域のゲート電極の周縁長の合計は3,803,596.80 μmであり,ダミーゲートの周縁長の合計は643,760.64 μmであり,

- h メモリセル領域のビットラインとセンスアンプ領域,選択・制御回路領域, ロジック領域,アナログ領域,I/O領域のゲート電極とダミーゲートは同 一の異方性ドライエッチングにて形成されている

- iことを特徴とするSDRAM。

- このうち、被告製品の半導体チップがSDRAMというDRAMの一種であること、DRAMは半導体メモリの一種であること、当該半導体チップにメモリセル、行(ロウ)デコーダ、センスアンプ、I/Oセレクタなどを有することについては、当事者間に争いがない。

- (11) 被告は、少なくとも被告製品 1, 2, 4 及び 5 を、日本国内において輸入し 又は譲渡している。

- 3 争点

10

15

25

当事者が、その内容を具体的に主張するのは、以下の点である。

- (1) 被告製品が本件発明の技術的範囲に属するか否か(争点1)

- ア 被告製品が,本件発明における「半導体集積回路装置」(構成要件1A,1 E,5B,5E等),「メモリ回路」(構成要件1B,1D)・「素子群」(構成 要件5A)を充足するか否か(争点1-1)

- イ 被告製品が、同一のエッチング工程により形成されたことを前提とする 「ライン状パターン」及び「回路パターン」(構成要件 1 A ないし 1 D, 5 A ないし 5 D) や「同一の異方性ドライエッチング工程によって形成されている」(構成要件 2 A, 6 A) を充足するか否か(争点 1-2)

- (2) 原告の損害・利得額(争点2)

- 4 争点に関する当事者の主張

10

15

20

25

(1) 被告製品が、本件発明における「半導体集積回路装置」(構成要件1A, 1E, 5B, 5E等)、「メモリ回路」(構成要件1B, 1D)・「素子群」(構成要件5A)を充足するか否か(争点1-1)

(原告の主張)

ア 「半導体集積回路装置」について

「半導体集積回路装置」には、システムLSIに限られず、DRAMも含む。

本件明細書において「ロジック回路が搭載されており、且つゲート電極及び配線が密に配列されてなるDRAM等のメモリー回路が搭載された半導体集積回路装置」(【0015】)との記載があるとおり、本件発明の「半導体集積回路装置」は、被告製品のようにメモリ回路以外の回路を含むDRAMやSDRAMも含むものとされている。また、本件発明の課題は「マスクパターンレイアウトの違いに起因して寸法ばらつきが生じることを防止すること」(【0009】【0013】)にあり、この課題は、DRAM等が搭載されたシステムLSIにおいてのみ存在するわけではない。本件発明の請求項

の文言や本件明細書によってもDRAM等が搭載されたシステムLSIにのみに上記課題が存在することを示唆する記載はない。むしろ、本件発明の課題解決手段は、本件明細書の記載(【0036】【0060】)によれば、チップ全体における単位面積当たりのゲート電極周縁長を大きく左右するものとして、単位面積当たりのゲート電極周縁長が大きい「特定回路」に着目し、このような「特定回路」の占有面積率が品種によって変動する場合でも、ダミーパターンを用いることでゲート電極周縁長のばらつきを抑制できるというものであるから、「特定回路」を備える半導体集積回路装置に広く妥当するものである。そのような「特定回路」には、DRAM内のメモリセルを構成する回路も含まれる。半導体集積回路装置における単位面積当たりのゲート電極周縁長を調整してCDロスを制御するという本件発明の課題解決手段(【0023】)も、DRAM等が搭載されたシステムLSIに対する手段に限定されていない。

本件明細書の記載(【0001】ないし【0003】)に照らせば、DRA M等が「搭載」された半導体集積回路装置とは、本件発明の課題を有する半導体集積回路装置の一例として示されたものである。また、DRAM等が「搭載」された半導体集積回路装置とは、半導体プロセスによりシリコンウェーハに回路パターンを形成することで製造される半導体チップに、DRAMとしての機能を有する構成及びその他の構成を含んでいる半導体集積回路装置を意味する。

被告が指摘する原告が審査段階で提出した意見書は、いずれも不明確なクレームの文言を明確にしたものである。これらの意見書において、「DRA M等の搭載率」等といったDRAM等が搭載された半導体集積回路装置についての説明があるが、それは本件発明の課題が見られる一例として説明されているにすぎず、これらに基づくものであると説明してクレームを補正したからといって、当該記載の内容にクレームが限定されるわけではない。

## イ 「メモリ回路」・「素子群」について

DRAM、SDRAMにおいて、メモリセルが「メモリ回路」、「素子群」 となる。

本件発明の課題は、「マスクパターンレイアウトの違いに起因して寸法ばらつきが生じる事態を防止」(【0023】)することにあり、「マスクパターンレイアウトの違い」があらわれるのは、単位面積当たりの周縁長が密である「微細な繰り返しパターンを有する素子群」(【0001】)を構成する回路パターンが含まれる場合である。上記アのとおり、DRAM等もDRAM等が搭載された「半導体集積回路装置」に含まれ、DRAMやSDRAMにおいて「微細な繰り返しパターンを有する素子群」は、メモリセルである。

## (被告の主張)

10

15

25

## ア 「半導体集積回路装置」について

本件明細書の記載(【0025】【0027】【0031】【0036】【0038】【0040】【0044】【0046】【0132】等)によれば、本件発明は、DRAM等が混載ないし搭載された「半導体集積回路装置」であることを前提に、DRAM等の搭載率ないし占有面積率の違い(DRAM搭載品種やDRAM非搭載品種といった品種の違い)に伴うマスクパターンレイアウトの違いに起因する寸法のばらつきを防止するものである。一般に、「搭載」とは、より大きな物に別の物を積み込んだり組み入れたりすることを意味するから、「DRAM」に「DRAM」を搭載するとはいわない。これらによれば、汎用DRAM自体は、本件発明の「半導体集積回路装置」には含まれない。

本件発明は、半導体集積回路装置におけるDRAM等の搭載率ないし占有面積率の違いに起因する寸法のばらつきという課題を前提とするものであるところ、DRAM等で100%構成される汎用DRAM等は、DRAM等の搭載率や占有面積率の違いが観念できない以上、本件発明の課題がそもそ

も存在しない。本件明細書の記載(【0058】【0059】)においても、汎用DRAM全体のゲート電極周縁長の値(2500mm/mm²)が最大値であることを前提として、DRAM占有面積率が80%である場合に相当する2000mm/mm²を電極周縁長の規格範囲の上限とし、1600~200mm/mm²を単位面積当たりのゲート電極周縁長の規格範囲として設定しているのであるから、汎用DRAMは、それ全体が「メモリ回路が形成されている領域」であり、「半導体集積回路装置」には該当しない。

本件発明の対応特許(米国特許第6794677号)には、DRAM等とメモリ回路が同義であることや、DRAM等(メモリ回路)はロジック回路とともに「半導体集積回路装置」に搭載される一部にすぎないことが明確に示されている。

10

15

25

汎用DRAMが「半導体集積回路装置」に該当しないとすることは、本件発明の出願経過とも整合する。出願人は、特許庁審査官の進歩性欠如の拒絶理由通知に対し、「請求項4(判決注:本件発明の請求項5)の発明を減縮し且つ明確にする補正を行ないましたので、拒絶理由1及び2は解消したものと思料いたします。尚、請求項4の補正の根拠は、出願当初の明細書の段落番号[0054]~[0055]、[0058]~[0060]の記載に基づきます。」などと記載された平成15年11月28日付け意見書や、「本願発明1は、上記の構成により、『ライン状パターンを有する回路パターン』の中に、単位面積当たりの周縁長が大きな『メモリ用ライン状パターン』が含まれ、『回路パターン』の中での『メモリ回路』の占有面積率が半導体集積回路装置の品種により大きく異なるマスクパターンレイアウト間において、次のような効果を生じます。…言い換えると、ダミーパターンを挿入することによって、異なるマスクパターンレイアウト間でパターンの粗密の程度を小さくします。このため、本願明細書の段落番号[0132]に記載されておりますように、『半導体集積回路装置の品種によりマスクパターンレイアウト

が大きく異なる場合にも、マスクパターンレイアウトの違いに起因してライン状パターンに寸法ばらつきが生じることを防止できる。従って、DRAM等の搭載率が用途又は仕様により異なるシステムLSIにおいても、ゲート電極又はメタル配線等の加工寸法をマスクパターンレイアウトと無関係に一定にできるので、動作マージンのバラツキが解消された半導体集積回路装置を実現できる』という格別の効果(以下、『本願発明1の効果』という)が得られます。」などと記載された平成16年3月25日付け意見書を提出している。

## イ 「メモリ回路」・「素子群」について

10

15

20

25

本件明細書の記載(【0001】【0003】【0015】【0054】)において、「メモリ回路」や「素子群」は、「半導体集積回路装置」に「搭載」ないし「混載」されるものであるとされ、同様に、「DRAM等」も、「DRA M等が搭載された半導体集積回路装置」やDRAM等の「搭載率」、「占有面積率」という記載があることから、これらは同義で用いられている。すなわち、「メモリ回路」や「素子群」は、「DRAM等」と同義であり、半導体装置(搭載部品)の回路を意味するものであり、そのような半導体装置(搭載部品)の全体をひとまとまりの単位とするものである。

このような解釈は、上記アのとおり、本件発明が、DRAM等の搭載率の違いに起因する寸法のばらつきを解決する技術であることに鑑みれば当然である。

本件明細書において、DRAM等の一部に過ぎない「メモリセル」が「メモリ回路」や「素子群」に該当するとの記載はなく、段落【0058】はメモリセルと汎用DRAMを明確に区別している。また、DRAM等の半導体装置(搭載部品)の回路は、メモリセル以外にセンスアンプや行デコーダなど多数の回路パターンから構成されるところ、これらは単体ではメモリ機能を果たすことができないから、機能的な意味においても半導体集積回路装置

に「搭載」するということができない。

(2) 被告製品が、同一のエッチング工程により形成されたことを前提とする「ライン状パターン」及び「回路パターン」(構成要件1 Aないし1 D、5 Aないし5 D)や「同一の異方性ドライエッチング工程によって形成されている」(構成要件2 A、6 A)を充足するか否か(争点1-2)

## (原告の主張)

10

15

20

25

本件発明2及び6以外の本件発明については、クレームの文言上、回路パターンが同一のエッチング工程で形成されているとの構成は含まれていないため、充足性の判断において、同一のエッチング工程で形成されていることは必要ではない。

本件発明1及びそれに従属する発明については、メモリ用ライン状パターンと基板表面から同一高さに存在するそれ以外のライン状パターンについて、その少なくとも一部が、マスクパターンレイアウトに依存した同一のエッチング工程で形成されていれば、本件発明の作用効果を奏し、同一のエッチング工程により形成されたといえる。同様に、本件発明5及びそれに従属する発明については、第1の回路パターンと、基板表面から同一高さに存在する第2の回路パターンについて、その少なくとも一部が、マスクパターンレイアウトに依存した同一のエッチング工程で形成されていれば、本件発明の作用効果を奏し、同一のエッチング工程により形成されたといえる。

#### (被告の主張)

本件発明における「半導体集積回路装置」(構成要件1A, 1E, 5B, 5E)においては、「ライン状パターン」や「回路パターン」(構成要件 $1A\sim 1D$ ,  $5A\sim 5D$ )は、全て「同一のエッチング工程」によって形成されることを前提としている。

被告製品に形成された「回路パターン」は、同一のエッチング工程によって 形成されたものではない。 (3) 原告の損害・利得額(争点2)

(原告の主張)

## ア 主位的請求

被告による平成27年7月からの被告製品の売上は、一年当たり150億円、同月から令和2年2月までの4年8か月で700億円(=150億円×4+150億円×8/12)を下らない。原告が本件発明の実施に対して受けるべき金銭の額は当該売上合計の1%にあたる7億円を下らない。本件における弁護士・弁理士費用は上記の5%に当たる3500万円を下らない。原告は、被告に対し、少なくとも7億3500万円の損害賠償請求権を有する(民法709条及び特許法102条3項)。原告は、本件訴訟において、そのうちの1億円を請求する。

#### イ 予備的請求

10

15

20

25

被告が、本件発明の実施料を支払うことを免れることによって得た利益と、 それを得られなかったことによる原告の損失との間に直接的な因果関係を 認めることができる。原告は、被告に対し、少なくとも7億円の不当利得返 還請求権を有する。本件における弁護士・弁理士費用は上記の5%に当たる 3500万円を下らない。原告は、本件訴訟において、そのうちの1億円を 請求する。

(被告の主張)

否認ないし争う。

# 第3 争点に対する判断

- 1 本件発明及びその意義

- (1) 本件明細書の発明の詳細な説明には、以下の記載があり、また、本件明細書には、別紙図面のとおりの図がある。(甲2)

- ア 発明の属する技術分野

「本発明は、半導体集積回路装置及びその製造方法に関し、特に、DRA

M (Dynamic Random Access Memory)等の微細な繰り返しパターンを有する素子群の混載が可能なシステムLSIにおける,MOS型トランジスタのゲート電極・配線又はメタル配線等のライン状パターンを形成するための技術に関する。」(【<math>OOO1】)

#### イ 従来の技術

10

15

20

25

「近年,例えばDRAMが混載された半導体集積回路装置として,搭載DRAM容量が 20 メガビットを超えるようなシステムLSI が量産化されつつある。」(【0002】)

「また、DRAM、SRAM(Static Random Access Memory)又はROM(Read Only Memory)等のメモリー回路の1個の半導体チップへの搭載率(チップ全体の面積に対するメモリー回路の面積の比率:以下、占有面積率と称することもある)が用途又は仕様により異なるシステムLSIをはじめとする半導体集積回路装置の製造工程においては、ユニット回路が単に繰り返し配列されているだけではなく様々なレイアウトが施されたマスクパターンの加工が求められている。」(【0003】)

「ところで、従来から、マスクパターンを用いて被加工膜に対してエッチングを行なうことにより得られるパターン(以下、加工パターンと称する)の形状又は寸法が、マスクパターンレイアウトつまり素子パターンの配置の仕方によって変化する現象が知られている。」(【0004】)

「前述のマスクパターンレイアウトに依存したパターン寸法の変動等の問題に対して、従来、近接効果又はローディング効果によってパターン寸法がマスクパターンレイアウトに依存して著しく変動すると考えられるようなマスク箇所でのみ、パターン寸法の変動を補正するような設計ルールが加えられていた。」(【0007】)

「また, DRAMの混載が可能なシステムLSIの製造においては、DR

AM搭載の有無又はDRAM占有面積率(チップ全体の面積に対するDRAMの面積の比率)に関係なく同一の加工方法又は加工条件が用いられてきた。」(【0008】)

### ウ 発明が解決しようとする課題

10

15

20

25

「しかしながら、LSIの微細化の進展に伴って、具体的には、集積回路 パターン寸法が  $0.25 \mu$  m以下、特に  $0.15 \mu$  m以下という微細化の進展に伴って、より高精度な寸法制御が求められるようになってきたため、マスクパターンレイアウトの違いに起因して生じる寸法ばらつきが無視できなくなりつつある。」(【 0009】)

「図8は、24メガビットのDRAMが搭載された半導体集積回路装置(以下、DRAM搭載品種と称する)、及びDRAMが搭載されていない半導体集積回路装置(以下、DRAM非搭載品種と称する)のそれぞれの製造においてレジストパターンをマスクとしてドライエッチングによりゲート電極を形成した場合における、エッチング前のレジストパターンの寸法と完成したゲート電極の寸法との差であるCD(critical dimension)ロスの頻度分布を示している。尚、図8に示す結果は、DRAM搭載品種及びDRAM非搭載品種のそれぞれの製造において同一のゲート電極加工プロセスを採用して得られたものである。また、CDロスの計算方法は、(エッチング前のレジストパターンの寸法) - (完成したゲート電極の寸法)である。」(【0010】)

「図8に示すように、各品種について同一のゲート電極加工プロセスを用いているにも関わらず、パターン寸法にマスクパターンレイアウト依存性が発生している。」(【0011】)

「すなわち,従来の半導体集積回路装置の製造方法においては,同一のゲート電極加工プロセスを採用したとしても,品種の違いに伴うマスクパターンレイアウトの違いによって,ゲート電極寸法がばらついてしまう。言い換

えると、ゲート電極寸法に品種依存性が発生してしまう。その結果、特定のマスクを用いて製造される半導体集積回路装置の特定の品種において、MO S型トランジスタの特性が設計仕様からずれてしまい、動作マージンが狭くなってしまうという問題が生じる。このような問題は設計ルールが0.18  $\mu$  m以下になると特に無視できなくなる。」(【0012】)

「前記に鑑み、本発明は、MOS型トランジスタのゲート電極・配線又はメタル配線等のライン状パターンを形成するときに、マスクパターンレイアウトの違いに起因して寸法ばらつきが生じることを防止することを目的とする。」(【0013】)

#### エ 課題を解決するための手段

10

15

20

25

「前記の目的を達成するために、本願発明者らは、マスクパターンレイアウトの違いによって寸法ばらつきが生じる原因について検討した。」(【0014】)

「その結果、CMOS(Complementaly Metal-Oxide Semiconductor)からなるロジック回路が搭載されており、且つゲート電極及び配線が密に配列されてなるDRAM等のメモリー回路が搭載された半導体集積回路装置においては、メモリ回路の占有面積率によってパターン寸法が変動することを見いだした。」(【0015】)

「また、マスクパターンレイアウトの違いによって寸法ばらつきが生じる現象は、被エッチング面積の大小つまりパターン面積の大小に依存して生じる前述のローディング効果とは性質が異なることを見いだした。さらに、この現象は、図8から明らかなように、チップ内部の局所的なパターンの粗密等に依存して生じるマイクロローディング効果とも異なり、チップ全体にわたってパターン寸法が変動するという新規な性質の現象であるということを見いだした。」(【0016】)

「ところで、前述のように、ゲート電極寸法等の加工寸法における品種依

存性はCDロスに起因して発生している。一方、現在のドライエッチング工程では、サイドエッチングを防止して異方性ドライエッチングを達成するために、側壁保護効果を有するエッチングガス(以下、デポガスと称する)を用いるか、又は側壁保護効果を有するエッチング反応生成物を形成している。例えば、ポリシリコン膜に対してドライエッチングを行なってゲート電極を形成する場合、エッチングガスとして塩素含有ガスが用いられると同時にデポガスとしてHBrガスがよく用いられる。このようにすると、ポリシリコン膜の側壁に、HBrとポリシリコンとの反応生成物であるSiBr4からなる揮発性の低い側壁保護膜が形成される。また、アルミニウム膜に対してドライエッチングを行なってアルミニウム配線を形成する場合、最近、デポガスとしてCHF3ガスがよく用いられる。ここで、フッ素含有ガスであるCHF3ガスは、側壁保護膜を形成するために添加された堆積性のガスである一方、アルミニウム膜のエッチングには寄与しない。」(【0017】)

10

15

20

25

「そして、マスクパターンレイアウトと無関係に同一のゲート電極加工プロセスを用いる場合において被エッチング膜の加工形状を側壁保護効果により制御しようとすると、保護対象となる被エッチング膜の側壁の面積が増大するに従って単位面積当たりの側壁保護効果が減少し、それによりCDロスが増大してしまうことを本願発明者らは見出した。」(【0018】)

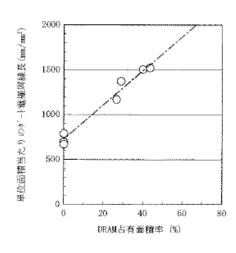

「図9は、DRAM非搭載品種を含む様々なDRAM占有面積率を有する品種における、単位面積当たりのゲート電極周縁長(ゲート電極の周縁部の長さ)とDRAM占有面積率との関係を示している。尚、図9のグラフにおいて、縦軸にとった「単位面積当たりのゲート電極周縁長」とは、所定の回路領域上におけるゲート電極の総周縁長を所定の回路領域の面積で割った値を意味する。ここで所定の回路領域はチップ全体であってもよい。」(【0019】)

「図9に示すように、DRAM占有面積率が増加するに従って、単位面積

当たりのゲート電極周縁長が増大する。」(【0020】)

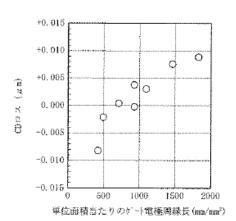

「また、図10は、様々な品種における、単位面積当たりのゲート電極周縁長とCDロスとの関係を示している。」(【0021】)

「図10に示すように、単位面積当たりのゲート電極周縁長が大きくなるとゲート電極寸法が細る(CDロスが正になる)一方、単位面積当たりのゲート電極周縁長が小さくなるとゲート電極寸法が太る(CDロスが負になる)。これは、単位面積当たりのゲート電極周縁長が大きくなるに従って、保護対象となる側壁の面積が増大し、それにより単位面積当たりの側壁保護効果が減少してしまうことが原因である。」(【0022】)

「そして、本願発明者らは、単位面積当たりのゲート電極周縁長が大きくなるに従ってCDロスが負の値から正の値に単調に変化していくこと(図10参照)に着目して、品種によらず単位面積当たりのゲート電極周縁長を所定の範囲に設定するか、又は、単位面積当たりのゲート電極周縁長の品種毎の違いに応じてプロセス条件を調整することによって、マスクパターンレイアウトの違いに起因して寸法ばらつきが生じる事態を防止できることを見いだした。」(【0023】)

#### オ 発明の実施の形態

10

15

20

25

「第1の実施形態の特徴は、ライン状パターンを有する回路パターンの配置領域にダミーパターンが挿入されており、それによってライン状パターンとダミーパターンとの合計の単位面積当たりの周縁長が所定の範囲に設定されていることである。」(【0053】)

「図1は,第1の実施形態に係る半導体集積回路装置におけるダミーパターン挿入前の回路パターンのレイアウトの一例を示しており,図2は,第1の実施形態に係る半導体集積回路装置におけるダミーパターン挿入後の回路パターンのレイアウトの一例を示している。尚,図1及び図2においては,ロジック回路の回路パターンを示しているが,第1の実施形態において,チ

ップ上にロジック回路に加えて、RAM又はROM等のメモリ回路が搭載されていてもよい。」(【0054】)

「図1に示すように、回路パターンは、MOS型トランジスタの活性領域パターン1及びゲート電極パターン2から構成されている。また、図2に示すように、活性領域パターン1及びゲート電極パターン2が設けられていない空き領域3に、短冊状又は線状のゲート電極ダミーパターン4が挿入されている。」(【0055】)

10

15

25

「このようにすると、チップ面積を増大させることなく、ゲート電極周縁 長を増大せることができる。具体的には、図1に示すダミーパターン挿入前 の回路パターンにおいては、単位面積当たりのゲート電極周縁長が500m m/mm<sup>2</sup>であるのに対して、図2に示すダミーパターン挿入後の回路パタ ーンにおいては、単位面積当たりのゲート電極周縁長が1600mm/mm <sup>2</sup>に増大している。 すなわち, 第1の実施形態においては, ダミーパターンの 挿入前の時点で、ゲート電極パターンが密集しているDRAM又はROM等 の占有面積率が小さい結果(或いはDRAM又はROM等が搭載されていな い結果),単位面積当たりのゲート電極周縁長が500mm/mm<sup>2</sup>と小さか った。そこで、図1に示す回路パターンにおけるゲート電極パターン2の単 位面積当たりのゲート電極周縁長を, DRAM又はROMの搭載率が大きい 他の品種における単位面積当たりのゲート電極周縁長に近づけるため、図2 に示すように、ゲート電極ダミーパターン4を大量に挿入することによって、 ゲート電極パターン2とゲート電極ダミーパターン4との合計の単位面積 当たりのゲート電極周縁長を1600mm/mm<sup>2</sup>と大幅に増大させてい る。」(【0056】)

「ところで、単位面積当たりのゲート電極周縁長の品種毎の違いに起因してゲート電極加工プロセス(具体的にはゲート電極エッチング)で生じる C Dロスのばらつきを、寸法測定又はレチクル製造等に伴う誤差範囲である 0

$\sim 0.003 \mu$  mに抑制するためには、単位面積当たりのゲート電極周縁長の品種毎の違いを  $500 \mu$  mm/mm²程度の範囲に抑える必要がある(図  $100 \pi$  mm/mm² ( $100 \pi$  mm/m

「一方、システムLSIでは、ゲート電極パターンが密集しているDRA M又はROM等の搭載率が品種によって大きく異なり、その結果、単位面積 当たりのゲート電極周縁長が品種毎に大きくばらつく。ここで、単位面積当 たりのゲート電極周縁長が最大となるのは、ゲート電極パターンが最も密集 するDRAMセルを有する汎用DRAMであって、その値は2500mm/mm²程度である。」(【0058】)

10

15

20

25

「従って、単位面積当たりのゲート電極周縁長の品種による違いを500 mm/mm²程度の範囲に抑えるために、規格範囲(前述の所定の範囲)を2000~2500mm/mm²程度と設定してもよい。しかしながら、ダミーパターン挿入前のレイアウトによっては、2000mm/mm²という単位面積当たりのゲート電極周縁長を満たすようにダミーパターンを挿入できない品種が存在する場合がある。現実的には、70%以上の占有面積率でDRAMが搭載されたシステムLSIは発生しないと想定できる。そこで、本実施形態においては、DRAM占有面積率が80%である場合に相当する2000mm/mm²を単位面積当たりのゲート電極周縁長の規格範囲の上限とし、1600~2000mm/mm²を単位面積当たりのゲート電極周縁長の規格範囲として設定した。」(【0059】)

「第1の実施形態によると、ゲート電極ダミーパターン4の挿入によって、チップ全体における単位面積当たりのゲート電極周縁長、つまり、ゲート電極パターン2とゲート電極ダミーパターン4との合計の単位面積当たりのゲート電極周縁長(図示しないメモリ回路が搭載されている場合にはそれに含まれる他のゲート電極パターンも加えた単位面積当たりのゲート電極周縁長)を所定の範囲に設定することができる。具体的には、所定の範囲とし

て、メモリ回路の単位面積当たりのゲート電極周縁長、つまり、最も大きい 単位面積当たりのゲート電極周縁長の70~100%を想定することが望 ましい。このとき、該規格が満たされるようにするためには、挿入されるゲ ート電極ダミーパターン4の単位面積当たりの周縁長(例えばゲート電極ダ ミーパターン4の周縁長を空き領域3の面積で割った値)は、メモリ回路の 単位面積当たりのゲート電極周縁長の70%以上である必要がある。このよ うにすると,半導体集積回路装置の品種によりマスクパターンレイアウトが 大きく異なる場合にも,チップ全体における単位面積当たりのゲート電極周 縁長を確実に所定の範囲に設定できる。例えば、メモリ回路等の特定回路は その単位面積当たりのゲート電極周縁長が大きいため、チップ全体における 単位面積当たりのゲート電極周縁長を大きく左右する。そして、チップ内に おける,このような特定回路の占有面積率が品種によって変動する場合にも, 前述のようにダミーパターンを用いることによって、チップ全体における単 位面積当たりのゲート電極周縁長のばらつきを抑制できる。その結果、マス クパターンレイアウトの違いに起因して寸法ばらつきが生じることを防止 できる。すなわち、ゲート電極パターン2を常に一定の寸法に精度良くエッ チング加工することが可能となる。従って、DRAM等の搭載率が用途又は 仕様により異なるシステムLSIにおいても、ゲート電極パターン2の加工 寸法をマスクパターンレイアウトと無関係に一定にできるので,動作マージ ンのバラツキが解消された半導体集積回路装置を実現できる。」(【0060】)

# カ 発明の効果

10

15

20

25

「本発明によると、半導体集積回路装置の品種によりマスクパターンレイアウトが大きく異なる場合にも、マスクパターンレイアウトの違いに起因してライン状パターンに寸法ばらつきが生じることを防止できる。従って、DRAM等の搭載率が用途又は仕様により異なるシステムLSIにおいても、ゲート電極又はメタル配線等の加工寸法をマスクパターンレイアウトと無

関係に一定にできるので、動作マージンのバラツキが解消された半導体集積 回路装置を実現できる。」(【0132】)

- (2) 以上によれば、本件発明は、DRAM (Dynamic Random Access Memory)等の微細な繰り返しパターンを有する素子群の混載が可能な半導体集積回路装置において、マスクパターンレイアウトの違いに起因して寸法ばらつきが生じるという課題に対し、その課題の原因がメモリ回路の搭載率や占有面積率によってパターン寸法が変動するというものであることを見出し、回路パターンの配置領域にダミーパターンを挿入することなどにより単位面積当たりのゲート電極周縁長を所定の範囲に設定し、それにより、マスクパターンレイアウトの違いに起因する寸法ばらつきを防止するという技術的意義を有するものであるといえる。

- 2 争点 1 1 (被告製品が,本件発明における「半導体集積回路装置」(構成要件 1 A, 1 E, 5 B, 5 E等),「メモリ回路」(構成要件 1 B, 1 D)・「素子群」(構成要件 5 A) を充足するか否か) について

10

15

20

25

- (1) 原告は、「半導体集積回路装置」(構成要件1A,1E,5B,5E)は、システムLSIに限られず、DRAMを含むものであり、DRAMを「半導体集積回路装置」とするとき、DRAM内のメモリセルが「メモリ回路」(構成要件1B,1D)・「素子群」(構成要件5A)となると主張する。

- (2) 半導体分野では、技術的な進歩に応じて、トランジスタの発明後に、IC(集積回路)、LSI(大規模集積回路)が開発されるに至った。LSIには複数の種類があり、大きく、メモリ、マイクロコンピュータ、ASIC、ASSPの4種類に区別されたり、メモリとロジック(マイクロコンピュータ、ASIC、ASSP)の2種類に区別されたりする。DRAMは、メモリ(記憶媒体)であり、書き込みと読み出し機能を持つLSIである。

システムLSIは、一個のチップに複数の素子を搭載するなどして複数の機能を有するものであり、そこに搭載される素子として、CPUやDRAMが含

まれ得る。(本項につき、乙7)。

(3) 本件明細書には、発明の属する技術分野として、「DRAM・・・等の微細な繰り返しパターンを有する素子群の混載が可能なシステムLSIにおける、MOS型トランジスタのゲート電極・配線又はメタル配線等のライン上パターンを形成するための技術に関する。」(【0001】)と記載されている。また、従来技術の課題の具体的な内容として、DRAMが搭載された半導体集積回路装置(DRAM搭載品種)とDRAMが搭載されていない半導体集積回路装置(DRAM非搭載品種)について、本件明細書の図(【図8】)のとおり、同一のゲート電極加工プロセスを用いているにもかかわらず、品種の違いに伴うマスクパターンのレイアウトの違いによってゲート電極寸法がばらついてしまい、特性が設計仕様からずれるなどの問題が生ずることが記載されている(【0010】~【0012】)。

そして、本件明細書によれば、本件発明は、マスクパターンレイアウトの違いに起因する寸法ばらつきが生ずることを防止することを目的とするものであり(【0013】)、その課題を解決する手段の欄において、発明者らがマスクパターンレイアウトの違いを踏まえて、見出した具体的な内容が記載されている。すなわち、DRAM非搭載品種を含む様々なDRAM占有面積率を有する品種における単位面積当たりのゲート電極周縁長(ゲート電極の周縁部の長さ)とDRAM占有面積率との関係について、本件明細書の図(【図9】)のとおり、DRAM占有面積率が増加するに従って、単位面積当たりのゲート電極周縁長が増大する(【0019】、【0020】)。また、単位面積当たりのゲート電極周縁長とCDロスとの関係を示す本件明細書の図(【図10】)のとおり、単位面積当たりのゲート電極周縁長が大きくなるとゲート電極寸法が細る(CDロスが正になる)一方、単位面積当たりのゲート電極周縁長が小さくなるとゲート電極寸法が太る(CDロスが負になる)。そして、その図に示されたとおり、単位面積当たりのゲート電極周縁長が大きくなるに従ってCDロスが負の値か

ら正の値に単調に変化していくことに着目して、品種によらず単位面積当たりのゲート電極周縁長を所定の範囲に設定するか、単位面積当たりのゲート電極周縁長の品種の違いに応じてプロセス条件を調整することによって、マスクパターンレイアウトの違いに起因して寸法ばらつきが生じる事態を防止できることを見出したとする(【0021】~【0023】)。

上記によれば、本件明細書には、従来技術の課題として、具体的には、DRAM搭載品種と非搭載品種とを比較した上で課題が生ずることが記載されており、その課題を解決するに当たっても、具体的には、DRAM非搭載品種を含む様々なDRAM占有面積率を有する品種について測定された数値によって見出された知見に基づき本件発明がされたことが記載されている。ここでは、その内容からも、DRAMその他の回路が搭載されるシステムLSIを念頭において検討がされて特定の知見が見出されたと認められる。他方、メモリであるDRAMについての固有の課題やそれについて何らかの知見が見出されたことは記載されていないし、本件明細書に具体的に記載されている上記の課題や見出された知見について、システムLSIとは技術的な内容が異なる、メモリであるDRAMについて、同様の課題があったことや、見出された上記の知見を適用できる旨の示唆もない。また、システムLSIの上記の課題や知見が、メモリであるDRAMについて、同様の課題があったことや、見出された上記の知見を適用できる旨の示唆もない。また、システムLSIの上記の課題や知見が、メモリであるDRAMでも同様に適用できることが技術常識であったことを認めるに足りる証拠もない。

また、本件明細書において、本件発明について、発明の属する技術分野(【0001】) や従来の技術として(【0002】、【0008】)、「システムLSI」が触れられており、実施例においても、「DRAM等」が「混載」ないし「搭載」された「半導体集積回路装置」という趣旨の記載が存在(【0025】【0027】【0031】【0036】【0038】【0040】【0044】【0046】【0132】等)して、システムLSIについての実施例が記載される一方で、メモリを「半導体集積回路装置」とする実施例の記載はないし、本件発明がメ

モリを「半導体集積回路装置」としても適用されることを示唆する記載もない。さらに、本件明細書に記載された実施例(【0058】【0059】)では、単位面積当たりのゲート電極周縁長の値について、汎用DRAM全体の値(2500mm/mm²)が最大値であることを前提として、DRAM占有面積率が80%である場合に相当する2000mm/mm²を単位面積当たりのゲート電極周縁長の規格範囲の上限とし、1600~2000mm/mm²を単位面積当たりのゲート電極周縁長の規格範囲として設定している。ここでは、汎用DRAMその他の素子が搭載されるシステムLSIにおいて、単位面積当たりのゲート電極周縁長につき、汎用DRAM全体を当然にひとまとまりとして捉えた上で規格範囲の上限を定めている。他方、汎用DRAM内部のメモリセルの単位面積当たりの電極周縁長など、汎用DRAM内部の構造についての説明はない。また、本件発明の課題との関係で汎用DRAM内部の構造を課題とする旨の記載もない。

10

15

20

25

前記(2)に照らせば、メモリであるDRAMとシステムLSIは、半導体製品という抽象的な枠組みでは共通するとしても、それら自体の内容や技術は異なり、その内部の構造も異なるものである。

本件明細書における,従来技術の具体的な課題や発明に当たり見出された内容,具体的な記載等に照らせば,本件発明は,システムLSIを念頭に置いているものであり,少なくとも,メモリであるDRAMが「半導体集積回路装置」(構成要件1A,1E,5B,5E等)に含まれることはないと解される。

(4) 被告は、本件明細書の記載(【0036】、【0060】)を挙げて、本件発明の課題解決手段として、単位面積当たりのゲート電極周縁長が大きいメモリ回路等の「特定回路」に着目したものであり、その「特定回路」にはメモリセルを構成する回路も含まれる旨主張する。しかし、本件明細書の実施例における上記各段落においては、DRAM等がメモリ回路等の「特定回路」に該当することを前提として、システムLSIについて発明を実現できることが記載され

ている。他方、その「特定回路」として、DRAM内のメモリセルが該当することについての示唆は全くないし、また、システムLSIにおいてDRAM等を「特定回路」とする記載により、DRAM内のメモリセルをDRAMにおける「特定回路」とすることが技術常識により明らかであったことを認めるに足りる証拠もない。被告の主張は、採用することはできない。

(5) 被告製品がDRAMの一種であるSDRAMであることについては当事者間に争いがない(前提事実(10))。したがって、被告製品は「半導体集積回路装置」(構成要件1A、1E、5B及び5E)に該当しない。

以上によれば、被告製品は、その余の構成要件について判断するまでもなく本件発明1及び5の技術的範囲に属さない。

3 被告製品は、上記2のとおり本件発明1及び5の技術的範囲に属さないことから、被告製品は、本件発明1の構成を前提とする本件発明2及び本件発明3、並びに、本件発明5の構成を前提とする本件発明6、本件発明7及び本件発明8の技術的範囲にも属さない。

#### 15 第4 結論

10

よって、原告の請求は理由がないからいずれも棄却することとし、主文のとおり判決する。

東京地方裁判所民事第46部

20 裁判長裁判官 柴 田 義 明

裁判官 佐 伯 良 子

25 裁判官佐藤雅浩は差支えのため署名押印できない。

裁判長裁判官 柴 田 義 明

(別紙)

# 被告製品目録

# 以下の製品名のSDRAM

5

- 1 MT 4 0 A 5 1 2 M 1 6 L Y 0 6 2 E : E

- 2 MT 4 0 A 1 G 8 S A 0 7 5 : E

- 3 MT40A2G4SA-075:E

- 4 MT40A512M16LY-062E IT:E

- $_{10}$  5 MT 4 0 A 5 1 2 M 1 6 L Y 0 7 5 : E

以上

15

図面

【図1】

【図2】

【図8】

【図9】

【図10】

31